Simulation VIP for GDDR6

Sign-off model for dozens of production designs.This Cadence® Verification IP (VIP) provides support for the JEDEC® Graphics Doub…

Overview

Sign-off model for dozens of production designs.

This Cadence® Verification IP (VIP) provides support for the JEDEC® Graphics Double Data Rate (GDDR6) SGRAM GDDR6 standard. It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for GDDR6 is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

The GDDR6 standard is is a modern type of synchronous graphics random-access memory (SGRAM) with a high bandwidth ("double date rate") interface designed for use in graphics cards, game consoles, and high-performance computation.

Supported specification: JEDEC JESD250, JESD250A, JESD250B, and JESD205C specification.

Key features

- Speed

- Supports up to 16Gbps with current vendor datasheets

- Device Density

- Supports a wide range of device densities from 8Gb to 32Gb

- Device Configuration

- Supports x16/x8 mode configuration; Supports Pseudo-channel (PC) mode configuration

- Bank Architecture

- 16B and BankGroup supported

- Clock

- CK (DDR), WCK (DDR, QDR), DFS (Clock frequency change)

- Supported Commands

- Write: WOM, WOMA, WDM, WDMA, WSM, WSMA, WRTR

- Read: RD, RDA, RDTR

- Precharge: PREab, PREpb

- Power down: PDE, PDX

- Self refresh: SRE, SRX

- Refresh: REFab, REFpb, REFp2b

- NOP, MRS, Activate, CAT

- Initialization

- Power-up sequence, Stable Power Sequence

- Interface Trainings

- Command address training, WCK2CK training, Read training, Write training

- Command Address Bus Inversion

- The number of CA lines driving a LOW level can be limited to 5 in 2-channel mode or 7 in PC mode for 8Gb, 12Gb and 16Gb densities and limited to 6 in 2-channel mode or 8 in PC mode for 24Gb and 32Gb densities

- Data Bus Inversion

- Data on the bus can be inverted during both read and write to save power. Data Bus Inversion the feature can be set through mode register

- Error Detection Code

- Supports Error Detection Code hold pattern, CRC, and special EDC in other states

- Tccd Reads and Writes

- Supports all combinations of Reads and Writes placed Tccd apart

- Self Refresh

- Supports Hibernate Self Refresh with VDDQ off

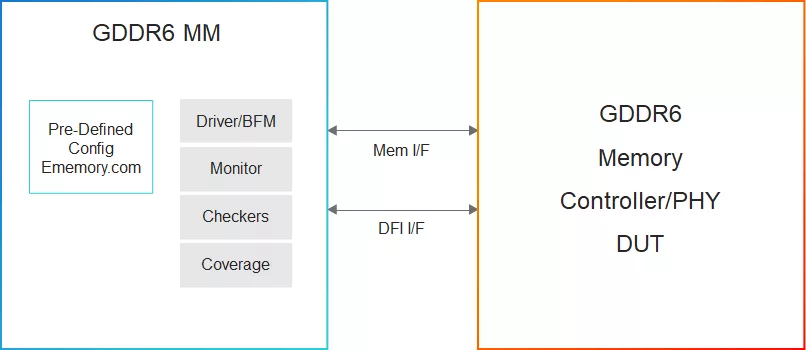

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about GDDR IP core

SPAD: Specialized Prefill and Decode Hardware for Disaggregated LLM Inference

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Designing the AI Factories: Unlocking Innovation with Intelligent IP

Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

The Growing Importance of AI Inference and the Implications for Memory Technology

Frequently asked questions about GDDR Interface IP

What is Simulation VIP for GDDR6?

Simulation VIP for GDDR6 is a GDDR IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this GDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.