100G Ethernet Verification IP

Comprehensive MAC-to-PCS Protocol Validation Solution The 100G Ethernet Verification IP (VIP) offers a robust and high-performanc…

Overview

Comprehensive MAC-to-PCS Protocol Validation Solution

The 100G Ethernet Verification IP (VIP) offers a robust and high-performance solution for validating the critical MAC-to-PCS datapath in 100 Gigabit Ethernet systems. Designed to ensure protocol compliance, the VIP facilitates the generation, transmission, reception, and monitoring of various Ethernet MAC frame types, all while adhering to IEEE 802.3ba and related standards. Whether you are working on IP, subsystem, or SoC-level verification, this VIP is your go-to solution for comprehensive Ethernet testing.

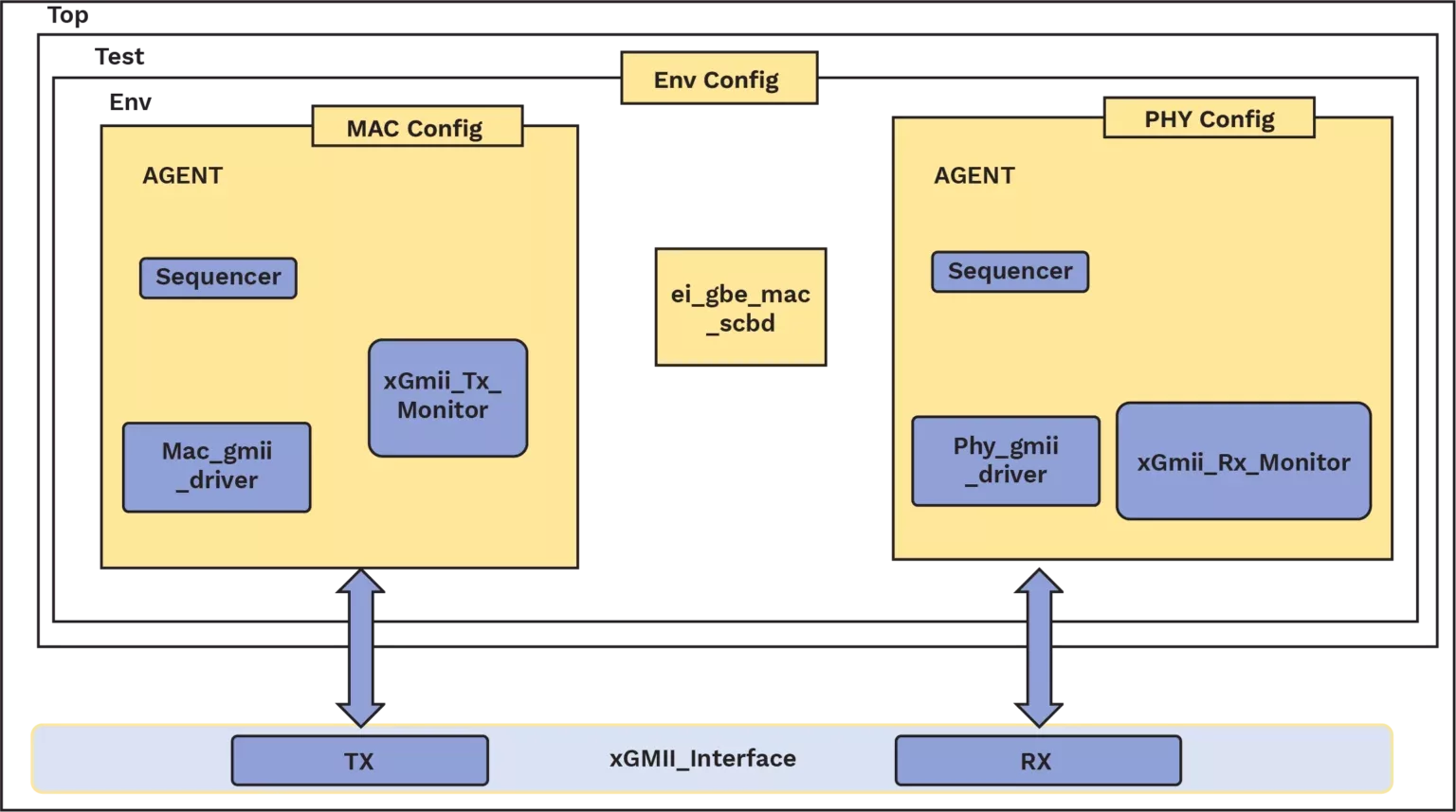

The 100G Ethernet VIP is built on a SystemVerilog foundation and follows the UVM 1.2 methodology, providing a flexible, modular architecture. Key components include:

- Sequencer & Sequence Library: Generates randomized and directed MAC frame traffic

- Driver (Transmitter): Converts MAC frames into encoded PCS blocks

- Monitor (Receiver): Captures and validates PCS-aligned data, reconstructing MAC frames

- Error Injection Engine: Introduces faults like sync header corruption and lane misalignment

- Assertions & Coverage Collectors: Ensures functional coverage for thorough validation

This layered structure allows the VIP to function as a transmitter, receiver, or passive monitor, adaptable to various verification environments.

Key features

End-to-End Visibility & Control

- The 100G Ethernet VIP provides complete visibility over the Physical Coding Sublayer (PCS), ensuring precise validation of encoding, lane distribution, synchronization, and alignment before data reaches the PMA/PMD layers.

Wide MAC Frame Support

- Standard Ethernet frames (64–1518 bytes)

- Jumbo frames (up to 9K bytes)

- VLAN-tagged and double-tagged (Q-in-Q) frames

- Pause and control frames

- Custom and error-injected frames for stress testing

Advanced Error Injection and Recovery

- Simulate real-world fault scenarios with error injection capabilities such as sync header corruption, lane misalignment, block disparity, and lane skew. Validate your system’s error recovery logic to ensure reliability under stress conditions.

Block Diagram

Benefits

Comprehensive Protocol Testing

- 64b/66b Encoding and Decoding

- Bit Error Rate (BER) Injection

- Elastic Buffer and Lane Alignment FIFO Behavior

- PRBS Pattern Generation

- FEC Bypass/Error Injection

- Real-time Error Monitoring and Fault Recovery Validation

Flexible Testing Modes

- Supports testing in active, passive, and mixed topologies, providing seamless integration for loopback and compliance tests.

What’s Included?

- 100G Ethernet VIP SystemVerilog source code

- UVM-compliant testbench components

- User Guide and Release Notes

- Test Plan and Sanity Test Cases

- Coverage Plan

- Sample Verification Environment

- Sanity test cases for quick bring-up and verification

- Example configurations for active, passive, and mixed topologies

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 100G Ethernet Verification IP?

100G Ethernet Verification IP is a Ethernet IP core from eInfochips listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.