TCAM Memory Model

TCAM Memory Model provides an smart way to verify the TCAM component of a SOC or a ASIC.

Overview

TCAM Memory Model provides an smart way to verify the TCAM component of a SOC or a ASIC. The SmartDV's TCAM memory model is fully compliant with standard TCAM Specification and provides the following features. Better than Denali Memory Models.

TCAM Memory Model is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

TCAM Memory Model comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports TCAM memory devices from all leading vendors.

- Supports all the TCAM commands as per the specification.

- Supports 100% of TCAM protocol standard.

- Supports following commands,

- Write

- Read

- Mask Write

- Mask Read

- Query

- Supports flexible selection of width and depth.

- Supports flexible masking.

- Supports single-cycle write, read and search operation.

- Supports match-found and match-done flags to check the provided key availability during search operation.

- Supports hardware reset.

- Checks for following,

- Availability of key

- Response time for the provided key

- Supports callbacks, so that user can access the data observed by monitor.

- Constantly monitors TCAM behavior during simulation.

- Quickly validates the implementation of the TCAM protocol.

- Supports callbacks for user to get command data on bus.

- Built in functional coverage analysis.

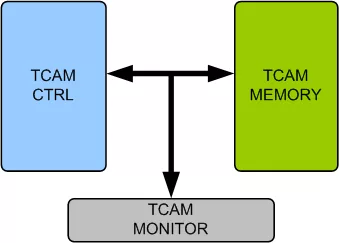

Block Diagram

Benefits

- Faster testbench development and more complete verification of TCAM designs.

- Easy to use command interface simplifies monitor control and configuration.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the TCAM testcases.

- Examples showing how to connect and usage of Model.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about FIFO / CAM IP core

On-Device AI Semiconductors & High-speed Interconnects in the Physical AI era

Serial Peripheral Interface. SPI, these three letters denote everything you asked for

Generating High Speed CSI2 Video by an FPGA

Improving Inter Integrated Circuits - From Sensor Hubs to Platform Management Solutions

Rigorous Framework for Hardware-Software Co-design of Embedded Systems

Frequently asked questions about FIFO / CAM IP cores

What is TCAM Memory Model?

TCAM Memory Model is a FIFO / CAM IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this FIFO / CAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this FIFO / CAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.