MIPI TX CPHY_v2.0 / DPHY_v2.5, 3-TRIO/1C4D, TSMC N5A, 1.2V, E/W orientation(ASIL-B)

MIPI D-PHY is a serial interface technology which is widely adopted in smartphones and other multimedia enabled mobile devices.

Overview

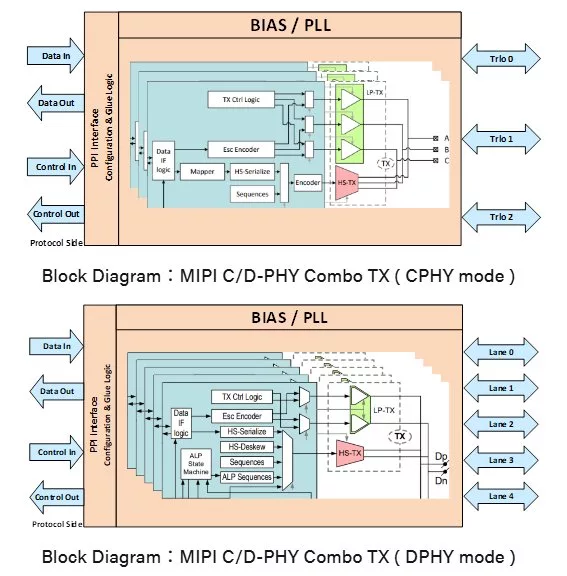

MIPI D-PHY is a serial interface technology which is widely adopted in smartphones and other multimedia enabled mobile devices. To further improve throughput over bandwidth limited channel, the C-PHY is developed and is delivering 2.28 bits per symbol over three-wire trio. As a MIPI Alliance contributor and leading Interface IP provider, M31 provides a silicon-proven, low-power and low cost C-PHY/D-PHY combo IP on various process nodes. Users can configure the PHY into D-PHY mode or C-PHY mode to support different applications using the same PHY. It is compliant to the PPI interface which allows seamless integration with upside controllers for Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols.

Key features

- Compliant with MIPI D-PHY v2.5 and C-PHY v2.0 specifications

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 6Gbps (6Gsps) per lane (per trio)

- Supports LS data rate of 10Mbps and Ultra-low power modes

- Supports D-PHY mode with 1 clock lane & up to 4 data lanes

- Supports C-PHY mode up to 3 trios for TX and 4 trios for RX

- Supports extra RX mode with 2 sets of 1 clock lane & up to 2 data lanes

- Supports Alternate Low-Power (ALP) mode

- Provides D-PHY swap function for clock and data lane

- Provides C-PHY swap function for trio

- Provides a stand-alone BIST module for at-speed mass production testing

- Certified with ASIL-B of ISO-26262

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 5nm | N5A | — |

Specifications

Identity

Provider

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI TX CPHY_v2.0 / DPHY_v2.5, 3-TRIO/1C4D, TSMC N5A, 1.2V, E/W orientation(ASIL-B)?

MIPI TX CPHY_v2.0 / DPHY_v2.5, 3-TRIO/1C4D, TSMC N5A, 1.2V, E/W orientation(ASIL-B) is a MIPI PHY IP core from M31 Technology Corp. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.