High-Speed JPEG Video Encoder

This “Dual-Core” High-Speed Baseline JPEG Encoder (Compression) core is capable of encoding video on-the-fly while producing stan…

Overview

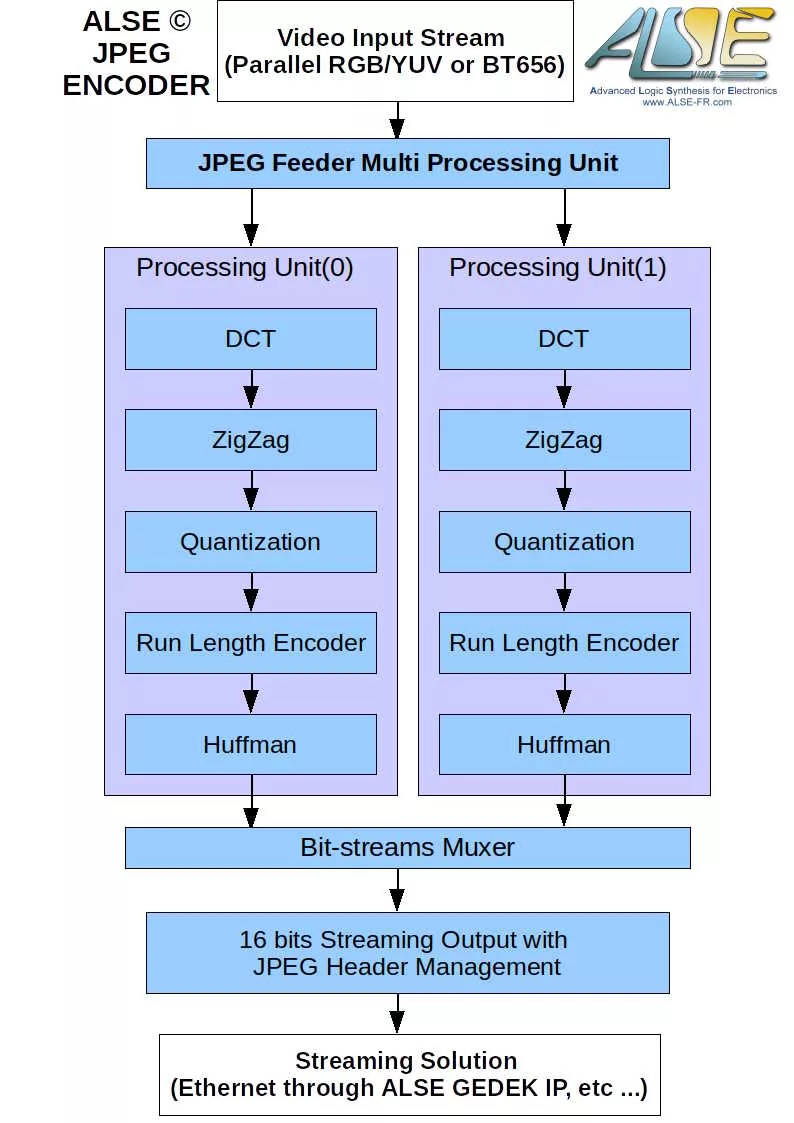

This “Dual-Core” High-Speed Baseline JPEG Encoder (Compression) core is capable of encoding video on-the-fly while producing standard JPEG compressed format. Its “Dual-core” architecture doubles the compression speed as compared to our standard baseline JPEG Encoder. The use of JPEG compression allows using very small FPGAs without external memory, leading to very economical systems, and our dual-core architecture allows high resolution and frame rates compression on low cost FPGAs.

Easy to use

Our core is compact and implements standard interfaces, so it can be used easily either as a standalone block, or as part of a Platform Designer system (or equivalent). Again : it does not require any embedded processor. It is small and efficient enough to fit easily in low cost and small FPGAs, like in the Altera Cyclone families, or the Lattice FPGA families (eg ECP3, ECP5, Certus-NX, CertusPro-NX, Crosslink-NX, Mach-XO5 etc) or the Microchip families (Igloo 2 or Polarfire for example).

Our simulation environment can be helpful to develop and the application that includes the JPEG encoder.

Key features

- Speed and Area-Optimized encoder engine suitable for both still image and real-time video compression.

- 8 bits (byte) Streaming output interface with Backpressure. Easy to connect to the ALSE Ethernet communication engine for example. Output format is 8x8 YUV Blocks (4:2:2).

- Supports any image resolution up to 64k x 64k.

- Suitable for still image and real-time video (streaming).

- Standard Huffman table.

- Dynamically configurable Quantization tables (up to 8 tables) for multiple levels of compression and quality.

- Dynamic choice of compression level (can be adjusted automatically).

- Can be easily integrated in a complete video system using the ALSE “Block to Raster” module, a Memory Frame Buffer and a Video Output Controller (RGB outputs for VGA, LCD; YUV BT656, etc … )

- Versatile. This IP can be used in all FPGA devices (internal memory blocks must be available).

- Compact.

- Fast : excellent Fmax on all FPGA families.

- First-class Technical Support (E-mail and Telephone, extended CET hours).

- Customization to specific needs available.

Block Diagram

Benefits

- More compact.

- More efficient than the competition.

- Faster. (better Fmax)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is High-Speed JPEG Video Encoder?

High-Speed JPEG Video Encoder is a Video Processing IP core from ALSE Advanced Logic Synthesis for Electronics listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.