Overview

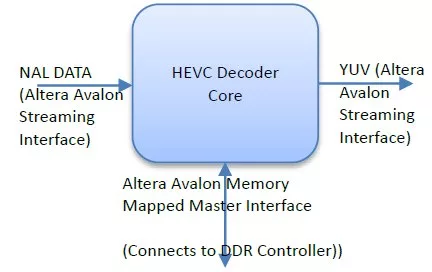

The H.265 HEVC Decoder System IPr is a highly optimized and parameterisable IP Core targeted exclusively at Intel FPGA technology. It is an ultra-low latency solution that is extremely robust with excellent error concealment, compliant with the ITU-T H.265 standard, designed for applications ranging from High End Broadcast, Contribution and Medical applications through to consumer grade applications.

Korusys provide both the IP core and, as an Intel FPGA Design Solutions Network Partner, experienced Design Services surrounding the core to implement the most efficient solution for each customer application. The IPr can be provided as a standalone netlist solution for integration into a customer’s design, or it can be customized and scaled to a particular implementation. A simple API is provided to ease integration.

This IPr is available as just the IP Core or as a package with our High Performance FPGA PCIe Accelerator Card.

Learn more about Video Processing IP core

This paper describes an FPGA-based high-definition video processing platform. The platform supports a wide range of applications including flat-panel TV, projection TV and video monitor.

Configurable Processors for Video Processing SOCs

Programmable FPGA devices are the perfect choice for interfacing with multiple high-resolution image sensors simultaneously...

A look at the design of multiprocessor systems-on-chips (MPSoCs) for video applications and how to optimize them for computational power and real-time performance as well as flexibility. Part 1: Architectural approaches to video processing

Building a high-performance, quad-channel H.264 encoder using low-cost, low-power FPGA architecture.

Adding to its growing portfolio of licensable silicon IP subsystems, ARC has announced five configurable video processing subsystems. The subsystems range from the smallest-size AV 402V to the highest-performance AV 417V, and support multi-standard video encoding and decoding at resolutions ranging from CIF to D1.