1G/10G TCP/IP Hardware Stack

The TCPIP-1G/10G core implements a TCP/IP Hardware Protocol Stack.

Overview

The TCPIP-1G/10G core implements a complete TCP/IP Hardware Protocol Stack. More capable than many offloading engines, it allows systems to connect to an Internet Protocol (IP) network and exchange data using the TCP protocol without requiring assistance from — or even the presence of — a system processor.

The core acts either as a server or a client and, without assistance from the host system, it autonomously opens, maintains, and closes TCP connections. The system integrating the TCPIP-1G/10G core can configure network parameters and preferences by accessing its control registers, and the core is then able to receive and send data via streaming data interfaces.

The highly configurable core can adapt to different applications and diverse system requirements. The maximum number of simultaneous TCP sessions is configurable at synthesis time; it can be as high as 32,768 for devices like data servers, or as small as 1 for edge devices requiring minimum silicon area and power. Further user options include implementing a DHCP client that allows the core to automatically be assigned an IP address, enabling or disabling support of the reassembly of out-of-order TCP packets data, and integrating a UDP hardware stack with multicast support (IGMPv3). Finally, users can choose the packet processing mode, either cut-through or store-and-forward. In cut-through mode, the payload data are delivered to the host system as they arrive without any internal packet buffering and before the packets’ integrity can be validated. As a result, the core operating in cut-through mode features extremely low latency and requires less memory, but it cannot reassemble out-of-order packets and it may deliver data that will subsequently be marked as corrupted. Under the store-and-forward mode of operation, the core will always deliver verified, in-order packets, but will have higher latency and require more memory resources.

The TCPIP-1G/10G core is rigorously verified and available in RTL source or as a targeted FPGA netlist. Its deliverables include a testbench, synthesis, and simulation scripts, and comprehensive user documentation.

Key features

- Complete TCP/IP Hardware Stack

- 10/100/1000, 2.5G, and 10G Ethernet Transmit and Receive

- TCP server or client with up to 32k simultaneous TCP sessions

- Autonomous and highly efficient TCP connection establishment, maintenance and teardown, retransmission, flow and congestion control

- Optional out-of-order TCP packet reassembly

- Checksums generation and validation

- IPv4 support

- Jumbo and Super Jumbo Frames

- ARP with Cache, ICMP (Ping Reply), VLAN (IEEE 802.1Q),

- UDP, IGMP, and DHCP (optional)

- Trouble-Free Operation

- Highly flexible thanks to runtime programmable options, including:

- Local MAC address, IP address, Gateway IP address, and IP subnet mask

- IP Address, & Port Filters

- Retransmission timeouts, limits, and enable/disable of fast retransmission

- Flow control and congestion control

- Window sizes, MSS

- Non-TCP/UDP IP traffic is optionally forwarded to the system via a dedicated port

- Highly flexible thanks to runtime programmable options, including:

- Easy SoC Integration

- Standardized AMBA interfaces:

- 64-bit AXI4-Stream for packet data

- 32-bit AXI4-Lite for CSR (APB3 optional)

- 256-bit AXI4 for external memory

- Separate clock domains for packet processing and CSR interfaces

- Independent from external memory type and controller, and from the ethernet MAC or PHY.

- Optionally pre-integrated with Intel, Xilinx, or other third-party eMAC core

- Standardized AMBA interfaces:

- Companion Cores from CAST

- DMA for integration as a memory-mapped peripheral

- MACsec protocol engine

- Low-Latency Ethernet MAC

- UDP/IP hardware stack

- TSN Endpoint, Switched Endpoint, and Switch

- Versions & Configuration Options

- Maximum number of simultaneous TCP sessions (up to 32K)

- Cut-through or store & forward processing

- Deliverables

- Synthesizable RTL or FPGA netlist

- Testbench & sample test cases

- UVM-based verification environment (optional)

- Simulation & synthesis scripts

- Documentation

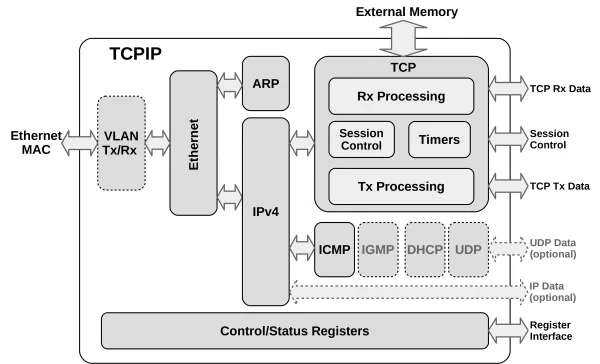

Block Diagram

What’s Included?

- Comprehensive user documentation,

- A sample integration testbench, and optionally a UVM-based verification environment

- Sample synthesis and simulation scripts

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 1G/10G TCP/IP Hardware Stack?

1G/10G TCP/IP Hardware Stack is a Ethernet IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.