Clock Buffer - X-FAB XT018-0.18µm BCD-on-SOI CMOS

The TS_CLKBUF_25pF_X8 transfers input clock signal to other digital or mixed-signal chips, which feature altogether a maximum loa…

Overview

The TS_CLKBUF_25pF_X8 transfers input clock signal to other digital or mixed-signal chips, which feature altogether a maximum load capacitance of 25pF.

The clock buffer keeps the output voltage rise and fall times within the range of 1.4ns to 3.1ns over the load capacitance range of 1pF to 26pF. This minimizes the electromagnetic emission spectrum owing to output voltage slew rate.

The TS_CLKBUF_25pF_X8 works with a supply voltage of 3.3V, and features an enable signal. It consumes an average current of 6.5mA for a 40MHz input clock with the maximum load capacitance of 25pF. It has a typical propagation delay of 6ns for the maximum load.

The TS_CLKBUF_25pF_X8 can be used together with the TES IP crystal oscillator TS_XOSC_40M_X8 to generate and transfer a 8MHz / 40MHz clock signal to external chips.

OPERATING CONDITIONS

| Parameters | Values |

| Junction temperature range | -40°C to 150°C |

| Supply voltage | 3.2V to 3.4V |

| Square-wave input frequency | 8MHz or 40MHz |

| Output load capacitance | 25pF max |

SPECIFICATION

| Parameters | Values |

| Supply peak current intensity, CL = 1pF – 26pF | 22.2mA to 112.2mA |

| Supply quiescent current intensity | 172nA max |

| Output voltage rise / fall time, rising from 10% of supply to 90% of supply and vice versa, CL = 1pF – 26pF | 1.4ns to 3.1ns |

Key features

- Max Load: 25pF total (including padcell and bondwire parasitics)

- Signal Integrity: Maintains tight rise/fall timing (1.4-3.1ns) across a wide load range (1pF to 26pF)

- Low Propagation Delay: 6ns typical delay at max load, ensuring fast response for real-time systems

- Efficient Power Use: 6.5mA average current at 40MHz with 25pF load, balancing performance and energy efficiency

- Enabling Control: Full support for enable input, allowing power-down in idle states

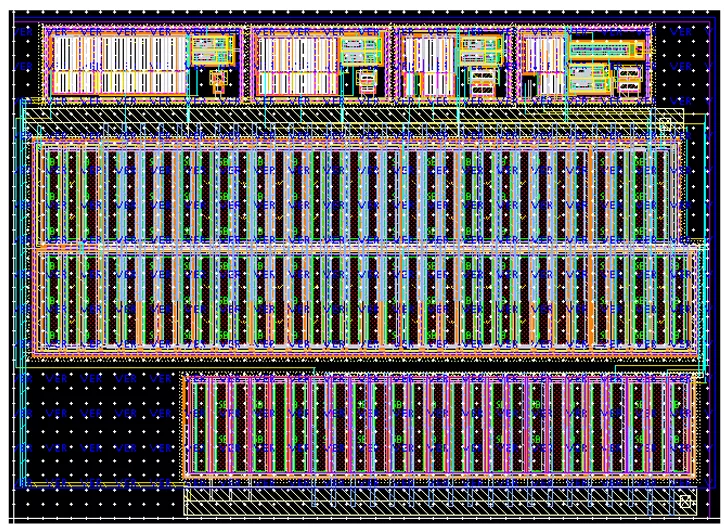

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Clock Generator IP core

Enhance circuit timing design with programmable clock generators (Part 1 of 2)

M31 on the Specification and Development of MIPI Physical Layer

Silicon-Accurate Fractional-N PLL Design

FPGA Implementation of DLX Microprocessor With WISHBONE SoC Bus

Mixed Signal Drivers for Ultra Low Power and Very High Power Applications

Frequently asked questions about Clock Generator IP cores

What is Clock Buffer - X-FAB XT018-0.18µm BCD-on-SOI CMOS?

Clock Buffer - X-FAB XT018-0.18µm BCD-on-SOI CMOS is a Clock Generator IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this Clock Generator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Clock Generator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.