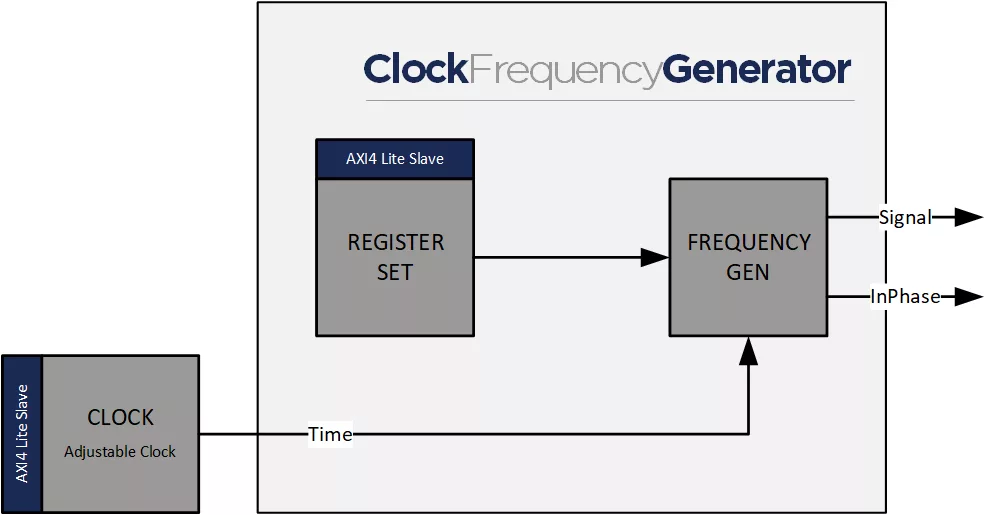

Learn more about Clock Generator IP core

Using our “Specman agent approach for the Mixed Verification” along with exploiting “real” feature of Specman version 8.2, we can introduce directed/constrained randomization to the frequencies needed for the analog modules which are interacting with the DUT (Design Under Test). This approach gives complete controllability over the clock frequencies, which can be directly randomized and modified on-the-fly from the testcase, as the scenario may demand.

As clocks speed increase and the number of clocks increases, a programmable clock generator may offer a better system and EMI design solution

MIPI is the abbreviation of "Mobile Industry Processor Interface". This article will introduce the physical layer specifications of MIPI architecture, and explain the features and benefits of D-PHY and C-PHY respectively. Then, the MIPI perspective on the development and challenges of automotive electronics and the professional MIPI technical services that M31 can provide will be shared.

Fractional-N PLLs are a useful class of PLLs and not well understood. This paper explains in simple terms how these differ from a regular integer PLL. Common applications are listed along with a brief description of the key performance parameter – jitter.

DLX is an open source microprocessor, it’s free and it has never been implemented in a commercial ASIC (Application Specific Integrated Circuit) design. The objective of this project is to use the DLX microprocessor implemented with Wishbone bus interface for a SoC (System-on-Chip) design.

Evolving niche markets, such as ICs for biomedical applications, are very challenging in respect to power consumption and on chip power dissipation, namely, wide range from ultra low power (ULP) functionality (<uW) where IC is battery powered, e.g. mobile micro transducers, to very high power (VHP, >5W), e.g. coded energy transfer from RFID¡¯s for remote sensing and animal tracking.