Sine Wave Frequency Generator

The Sine Wave Frequency Generator is a time and frequency aligned sine wave frequency generator allowing any frequency to be gene…

Overview

The Sine Wave Frequency Generator is a time and frequency aligned sine wave frequency generator allowing any frequency to be generated between 1Hz and 200kHz adjustable in 1Hz steps. It uses the vendor's Adjustable Clock core as source for source synchronous frequency generation. It provides either a parallel DAC interface or a serial highly configurable SPI interface to access a DAC.

The IP core comes with a Linux Driver (the same driver as for the Frequency Generator)

Key features

- Configurable frequency signal generation (1-200kHz (depends on DAC sampling rate))

- Configurable polarity (positive or negative zero crossing and PPS boundary)

- Output delay compensation

- Alignment of the frequency generator to an input time (frequency and phase)

- Automatic realigning of the frequency generator on time jumps and frequency changes

- Continuous generation until disabled

- Configurable DAC Sample width

- Configurable DAC Sampling rate

- Optional DAC Sample scaling

- Optional DAC Sample offset

- SPI DAC Controller

- AXI4Lite register set or static configuration

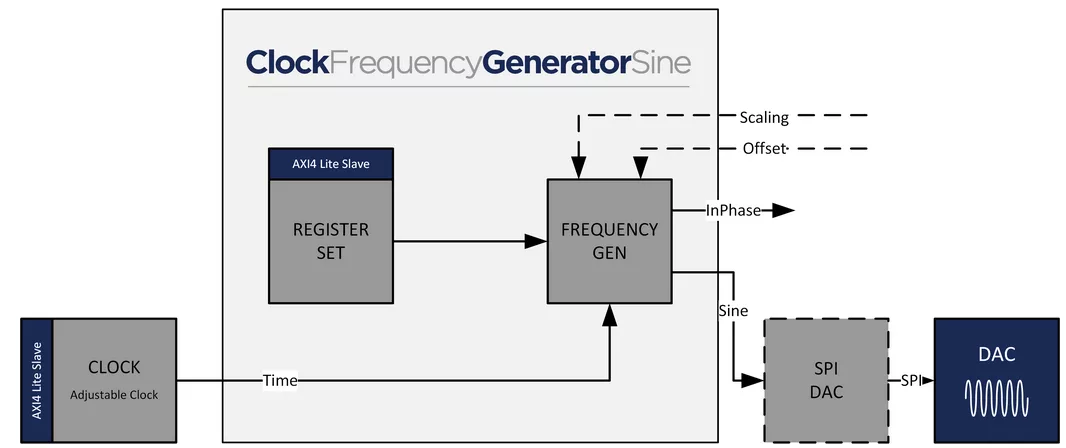

Block Diagram

Benefits

Generating

- Frequency aligned with NetTimeLogic’s Clock (frequency and phase at second crossing)

- Output delay compensation takes also external delays like DAC, SPI, RC into account

- Configurable DAC Data width

- Configurable DAC Sampling rate

- Optional Scaling and DC Offset

- Auto phase realignment on time jumps

Performance

- Output signal max frequency is ~200kHz at 2MSPS DAC sam-pling

Portability

- Vendor independent, written in plain VHDL

- Low footprint and low frequency requirements

Modularity and scalability

- Simple time format can be also sourced by third-party clock core Slim and standardized interfaces are used

Configuration

- No CPU required, standalone configuration with signals

Axi4 lite slave support, for configuration

Applications

- Distributed data acquisition

- Test and measurement

- Robot control

- Substation automation

- Ethernet based automation networks

What’s Included?

- IP core in plain VHDL

- Testbench in plain VHDL

- Reference Design

- Top level VHDL file

- Timing Constraint SDC files

- Vivado/Quartus Project file

- Linux Driver

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Clock Generator IP core

Enhance circuit timing design with programmable clock generators (Part 1 of 2)

M31 on the Specification and Development of MIPI Physical Layer

Silicon-Accurate Fractional-N PLL Design

FPGA Implementation of DLX Microprocessor With WISHBONE SoC Bus

Mixed Signal Drivers for Ultra Low Power and Very High Power Applications

Frequently asked questions about Clock Generator IP cores

What is Sine Wave Frequency Generator?

Sine Wave Frequency Generator is a Clock Generator IP core from NetTimeLogic GmbH listed on Semi IP Hub.

How should engineers evaluate this Clock Generator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Clock Generator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.