64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

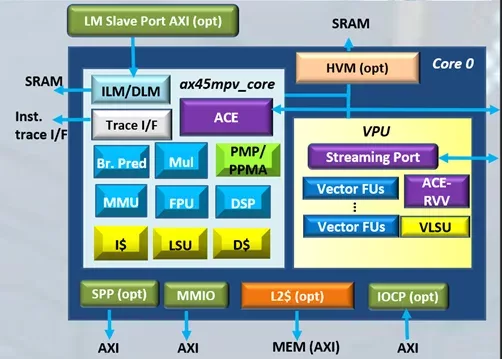

AndesCore™ AX45MPV 64-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeSta…

Overview

AndesCore™ AX45MPV 64-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture. It supports RISC-V standard “G (IMA-FD)”, “C” 16-bit compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector) extensions, and Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions. It features MMU for Linux based applications, dynamic branch prediction for efficient branch execution, dual-issue of common instruction pairs, level-1 instruction/data caches and local memories for low-latency accesses. The AX45MPV symmetric multiprocessor supports up to eight cores and a level-2 cache controller with instruction and data prefetch. Coherence Manger ensures data coherence among CPU accesses and IO transactions from cacheless bus masters. The AX45MPV contains a powerful VPU with up to 1024-bit VLEN and DLEN, and is excellent for computations involving large arrays of data such as computer vision, digital signal processing, image processing, machine/deep learning, and scientific computing. Other features include ECC for level-1/2 memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™ and StackSafe™, and PowerBrake and WFI for power management.

AndeStar™ V5 Architecture

| Key Features | Benefits |

|---|---|

| RISC-V RV64 GCBPV |

|

| Andes Extended Instructions | Andes exclusive performance and functionality enhancements |

| MMU and Sv39/Sv48 virtual memory translation | For Linux and advanced operating systems with protection between kernel and user program |

| 64-bit CPU architecture | Enabling software to utilize the memory spaces far beyond the 4G byte limit of 32-bit CPUs |

| Machine (M), optional User (U) and Supervisor (S) Privilege levels | Embedded systems with privilege protections |

CPU Core

| Key Features | Benefits |

|---|---|

| 5.86 CoreMark/MHz, 3.39 DMIPS/MHz | Superior performance-per-MHz |

| 8-stage dual issue in-order superscalar pipeline | Superior performance-efficiency, while allowing for high speeds |

|

Extensive branch predication features

|

|

|

|

| Physical Memory Protection (PMP), configurable up to 32 regions | Basic read/write/execute memory protection with minimum cost |

| Programmable Physical Memory Attribute (PMA), configurable up to 16 regions |

Configurable memory attributes:

|

| Performance monitors | Program code performance tuning |

| StackSafe™ hardware stack protection |

|

| PowerBrake technology | Performance throttling to digitally reduce power consumption |

| QuickNap™ technology | Fast power-down/wake-up support for cache |

Memory Subsystems

| Key Features | Benefits |

|---|---|

|

Level-1 I-Cache & D-Cache

|

|

|

Level-2 I/D Unified Cache

|

|

|

ILM & DLM

|

|

|

HVM

|

|

|

MemBoost

|

|

| Optional ECC error protection with SRAM interface | Code and data integrity protection |

| Bus master port: AXI with 128/256/512-bit data, I/D joint or separate bus | High throughput with wide data path |

| BUS Slave Port: AXI with 128/256/512-bit data, for ILM/DLM accesses | Efficient data transfer between CPU and SoC masters |

| Core/bus clock ratio of N:1 | Simplified SoC integration |

Multicore Cache Coherence

| Key Features | Benefits |

|---|---|

|

|

Vector Processing Unit (VPU)

| Key Features | Benefits |

|---|---|

|

|

|

|

|

|

Platform-Level Interrupt Controller (PLIC)

| Key Features | Benefits |

|---|---|

|

Implements RISC-V PLIC specification

|

Interrupt handling for SoC with multiple processors |

|

Enhanced interrupt features

|

Complete hardware preemption support |

Debug Support

| Key Features | Benefits |

|---|---|

| Implements RISC-V debug specification v1.0 | Supported by industry debug tool suppliers |

| JTAG Debug Port | Industry-standard support |

| Embedded Debug Module with up to 8 triggers | Flexible configurations to tradeoff between gate count and debugging capabilities |

| Exception redirection support | Entering debugger upon selected exceptions without using breakpoints |

| RISC-V Trace 1.0 Instruction Trace interface | Supported by Andes tools |

*MMU and HVM features are available in 2023 Q4

Key features

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU)

- Symmetric multiprocessing up to 8 cores

- Level-2 cache and coherence support

- High bandwidth vector local memory (HVM)

- AndeStar™ V5 Instruction Set Architecture (ISA)

- Compliant to RISC-V GCBPV extensions

- Andes performance extension

- Andes CoDense™ extension for further compaction of code size

- Full-arithmetic BF16 vector/scalar instructions with mode bit control

- Separately licensable Andes Custom Extension™ (ACE) for customized scalar and vector instruction

- 64-bit architecture for memory space over 4GB

- Branch predication to speed up control code

- Linux-capable Memory Management Unit (MMU)

- Physical Memory Protection (PMP) and programmable Physical Memory Attribute (PPMA)

- Andes-enhanced Platform-Level Interrupt Controller (PLIC) for a wide range of system events and real-time performance

- Multiprocessing up to 8 cores with hardware managed data coherence

- Configurable VPU vector length (VLEN) and datapath length (DLEN)

- Platform-Level Interrupt Controller (PLIC) support with easy arrangement of preemptive interrupts

- ECC or Parity for SRAM error protection

- StackSafe™ hardware to help measuring stack size, and detecting runtime overflow/underflow

- Versatile configurations to tradeoff between core size and performance requirements

- PowerBrake and WFI (Wait For Interrupt) for different power saving occasions

Block Diagram

Applications

- Computer vision

- Digital Signal Processing

- Image Processing

- Machine/Deep learning acceleration

- Scientific Computing

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 64-bit RISC-V Multicore Processor with 1024-bit Vector Extension?

64-bit RISC-V Multicore Processor with 1024-bit Vector Extension is a CPU IP core from Andes Technology Corp. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.