<4Gbps Low Power D2D Interface in TSMC 16nm & 28nm

A

Overview

A <4Gbps, Wide I/O Compatible, Die to Die Interface in TSMC 16nm and 28nm.

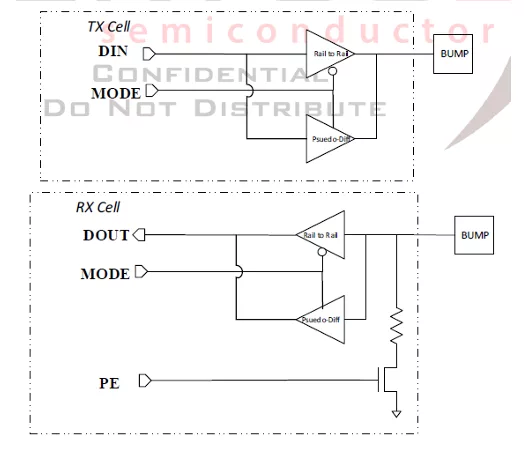

This silicon proven die to die interface includes IP in both TSMC 16nm FFC/FFC+ and 28nm HPM/HPC/HPC+. The I/O cells for both versions of the library are defined as TX only and RX only. The cells have two modes of operation: standard full rail to rail swing or a custom low noise psuedo-differential interface. The RX cells have a weak pull-down feature. The library is designed for Flip-chip/Die to Die packaging only, with no Wirebond option. Both library options have a common power bus architecture that when the cells are abutted, will feed through. There are no Power or Ground Pad/Cells, however all VDD and VSS connections will be made to the Core domain in upper metals. Both library options are ultra-low power, have a small footprint, MCM compliant, and have HBM & CDM robustness.

Operating Conditions for 16nm

| Parameter | Value |

| VDDIO | 0.8V |

| I/O Device | 1.8V |

| Core | Use SVT Only |

| Cell Size | 50x28.06um |

| BEOL | M8 & below |

| VDD Core | 0.8V +/- 10% |

| Temperature | -40C to 125C |

| Operational Bit Rate | 2Gbps1 |

Operating Conditions for 28nm

| Parameter | Value |

| VDDIO | 0.9V |

| I/O Device | 1.8V |

| Core | Use SVT Only |

| Cell Size | 50x25um |

| BEOL | M8 & below |

| VDD Core | 0.9V +/- 10% |

| Temperature | -40C to 125C |

| Operational Bit Rate | 2Gbps1 |

Cells for 16nm D2D

| Cell Name | Width | Description |

| UF_TX | 50x25um | TX Cell |

| UF_RX | 50x25um | RX Cell |

Cells for 28nm D2D

| Cell Name | Width | Description |

| UD_TX | 50x30.5um | TX Cell |

| UD_RX | 50x30.5um | RX Cell |

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | 28nm 280 nm | — |

Specifications

Identity

Provider

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is ?

is a Custom IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.