Overview

The 2.5GMAC IP core supports the ability to transmit and receive data between a host processor and an Ethernet network. The main function of the Ethernet MAC is to ensure that the Media Access rules specified in the 802.3 IEEE standard are met while transmitting a frame of data over Ethernet. On the receiving side, the Ethernet MAC extracts the different components of a frame and transfers them to higher applications through the FIFO interface.

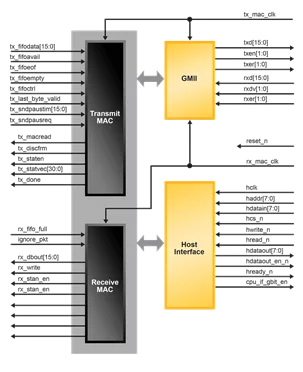

The 2.5GMAC IP core transmits and receives data between a client application and an Ethernet network. The main function of the Ethernet MAC is to ensure that the Media Access rules specified in the 802.3 IEEE standard are met while transmitting and receiving Ethernet frames.

On the receiving side, the Ethernet MAC extracts the different components of a frame and transfers them to high-er applications through the client FIFO interface. The data received from the GMII interface is first buffered until sufficient data is available to be processed by the Receive MAC (Rx MAC).

The Preamble and the Start-of-Frame Delimiter (SFD) information are then extracted from the incoming frame to determine the start of a valid frame. The Receive MAC checks the address of the received packet and validates whether the frame can be received before transferring it into the FIFO. Only valid frames are transferred into the FIFO (runts and fragments are discarded). The Rx MAC also provides a statistics vector on a per packet basis that can be used by the application. The 2.5GMAC IP core always calculates CRC to check whether the frame was received error-free.

On the transmit side, the Tx MAC is responsible for controlling access to the physical medium. The Tx MAC reads data from an external client Tx FIFO, formats this data into an Ethernet packet and passes it to the GMII module.

The Tx MAC reads data from the Tx Client FIFO when the client indicates a packet is available, and the Tx MAC is in its appropriate state. The Tx MAC pre-fixes the Preamble and the Start-of-Frame Delimiter information to the data and appends the Frame Check Sequence at the end of the data.

Learn more about Ethernet IP core

Rambus, having successfully served the data center, enterprise and infrastructure markets with line rate MACsec and IPsec products (Secure Networking), adds two new solutions for securing UET transport protocol with TSS.

Ultra Accelerator Link (UA Link) standard has been specified to enable the creation of systems comprised of multiple nodes targeting AI applications.

As factories, process plants, and robotics platforms become increasingly intelligent and interconnected, the demand for stable, low-latency data links has pushed Ethernet deeper into embedded systems. However, since designing Ethernet connectivity into industrial chips comes with its technical and logistical hurdles, engineers may face challenges when implementing Ethernet in industrial designs.

Ultra Ethernet, designed for scale out architectures, is an open, interoperable, high-performance protocol solution tailored for AI, supported by industry leaders across switch, networking, semiconductor, and system providers, as well as hyperscalers.

At the recent ECOC 2025 conference in Copenhagen, Cadence showcased its key role in enabling the future of AI infrastructure with live silicon demonstrations of several essential IP technologies for emerging 800G and 1.6T networks. Powered by Cadence's 224G SerDes IP, Cadence's Ultra Accelerator Link (UALink 1.0) scale-up and Ultra Ethernet scale-out networking solutions deliver the performance, flexibility, and interoperability needed for next-generation AI factories and hyperscale data centers.

As artificial intelligence and high-performance computing (AI/HPC) reshape industries, the need for robust, scalable, and secure connectivity has never been greater. Built from tightly integrated CPUs, GPUs, and SmartNICs, today’s compute clusters demand high-throughput, low-latency networks that can scale from die-to-die to multi-rack deployments.