Rambus Delivers PCIe 6.0 Controller for Next-Generation Data Centers

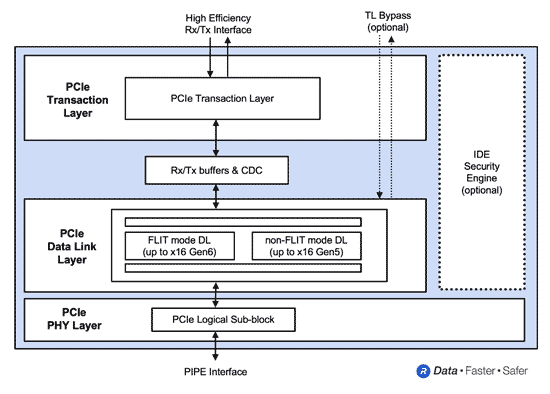

SAN JOSE, Calif. – Jan. 26, 2022 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the availability of its PCI Express® (PCIe®) 6.0 Controller. The PCIe specification is the interconnect of choice across a broad landscape of data-intensive markets including data center, AI/ML, HPC, automotive, IoT, defense and aerospace. Optimized for power, area and latency, the Rambus PCIe 6.0 controller delivers data rates up to 64 Gigatransfers per second (GT/s) for high-performance applications. In addition, the controller provides state-of-the-art security with an Integrity and Data Encryption (IDE) engine that monitors and protects PCIe links against physical attacks.

“The rapid advancement of AI/ML and data-intensive workloads requires that we continue to provide higher data rate solutions with best-in-class latency, power and area,” said Sean Fan, chief operating officer at Rambus. “As the latest addition to our portfolio of industry-leading interface IP, our PCIe 6.0 Controller offers customers an easy to integrate solution that delivers both performance and security for advanced SoCs and FPGAs.”

Key features of the Rambus PCIe 6.0 Controller include:

- Supports PCIe 6.0 specification including 64 GT/s data rate and PAM4 signaling

- Supports fixed-sized FLITs that enable high-bandwidth efficiency

- Implements low-latency Forward Error Correction (FEC) for link robustness

- Internal data path size automatically scales up or down (256, 512, 1024 bits) based on max. link speed and width for reduced gate count and optimal throughput

- Backward compatible to PCIe 5.0, 4.0 and 3.0/3.1

- Supports Endpoint, Root-Port, Dual-Mode and Switch port configurations

- Integrated IDE optimized for performance

More Information:

For more information on the PCIe 6.0 Controller, please visit our website. Or, view the PCIe 6.0 specification online.

Related Semiconductor IP

- PCIe 6.0 Retimer Controller with CXL Support

- PCIe 6.0 (Gen6) Premium Controller with AMBA bridge and LTI & MSI Interfaces

- PCIe 6.0 (Gen6) Premium Controller with AMBA bridge

- PCIe 6.0 (Gen6) Premium Controller

- PCIe 6.0 (Gen6) Premium Controller EP/RP/DM/SW 128-1024 bits with AMBA bridge and Advanced HPC Features (Arm CCA)

Related News

- Rambus Delivers PCIe 6.0 Interface Subsystem for High-Performance Data Center and AI SoCs

- PLDA Announces Robust Verification Toolset, Increasing Design Accuracy and Reducing Time-to-Production for Next Generation SoCs with CXL, PCIe 6.0 or Gen-Z Interconnect

- Alphawave and PLDA Announce a Collaboration to Create Tightly-Integrated Controller and PHY IP Solutions for Interconnects Including PCIe 5.0, CXL and PCIe 6.0

- Avery Design Systems and Rambus Extend Memory Model and PCIe VIP Collaboration

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud