OPENEDGES Completes the Tapeout of the 7nm HBM3 Memory Subsystem (PHY & Memory Controller) Test chip

Seoul, South Korea, March 23rd, 2023 --- OPENEDGES Technology, Inc. (OPENEDGES) today released a detailed update on the successful completion of the first tape out of an advanced 7nm process technology test chip for its HBM3 memory subsystem IP, including the PHY and memory controller. This update provides in-depth insights into the tape-out that represents the completion of the design phase, the beginning of silicon characterization and validation, and the expansion pathway to more silicon-proven IPs supporting the most up-to-date JEDEC DRAM standards.

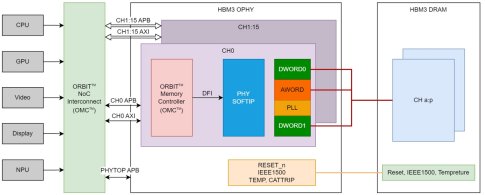

The OPENEDGES 7nm HBM3 memory subsystem IP testchip was designed in compliance with the JEDEC JESD238 HBM3 standard, delivering up to 8.4Gbps data rates per IO in a 2.5D integration platform. The HBM3 PHY IP has the capability to support up to 16 independent and asynchronous channels, each with 2x32-bit DWORD pseudo-channels. Additional features include multiple frequency set points (FSPs), DBI, ECC, SEV, and Parity (data and command/address parity), as well as lane repair, also known as Interconnect Redundancy Remapping, which detects, repairs, and remaps repairable interconnect issues automatically, making them transparent to the memory controller.

Moreover, it’s equipped with a proprietary microcontroller for firmware-based training and a firmware-based API to work with DRAM’s IEEE 1500 for training and testing. Optimized traffic monitoring with power-down and self-refresh states improves power efficiency, and the out-of-order scheduling algorithm, combined with the highly optimized pipeline architecture, provides an efficient solution for applications requiring high memory bandwidth, particularly in the fields of artificial intelligence (AI), machine learning (ML), and general-purpose graphics processing units (GPGPU).

“We are very proud of the team in completing the development of this complex, large-scale IP, starting only from the JEDEC specification and taking all the way through the physical implementation of a test chip,” said Farhad Haghighi Zadeh, Principal Engineer at The Six Semiconductor of OPENEDGES Technology and Design Lead for the HBM3 program. “This project demonstrated our excellence in execution through cross-team collaboration.”

“As HBM3 can process vast amounts of data quickly, it is becoming more essential and recognized as an advanced technology that is necessary for the faster processing of big data,” said Sean Lee, the CEO of OPENEDGES Technology. “Taking advantage of OPENEDGES’ past success with various tape-outs, we will continue collaborating with our client to silicon-prove the HBM3 7nm memory subsystem IP and introduce it to the market”.

By incorporating an architecturally optimized approach to analog mixed-signal design and partitioning across its PHY IP portfolio, OPENEDGES is able to provide maximum ease of integration for its hard-IP components and enable the latest DDR standards even on older technology nodes. The PHY IPs offered by OPENEDGES support JEDEC-compliant standards, such as HBM3, GDDR6, and LPDDR5X/5/4X/4, in multiple foundries and technology nodes.

Image 1: OPENEDGES’ HBM3 Memory Subsystem

About OPENEDGES Technology, Inc.

OPENEDGES Technology, Inc. is a premier provider of memory subsystem IPs for the semiconductor industry. They offer a wide range of state-of-the-art solutions, including DDR memory controllers, DDR PHY, NoC interconnect, and NPU IPs that are widely adopted by customers worldwide. Their IPs comply with JEDEC standards, including LPDDR5x/5/4x/4/3, DDR5/4/3, GDDR6, and HBM3, ensuring their compatibility with the latest DDR technology trends. In 2019, they acquired The Six Semiconductor, Inc. (TSS), specializing in high-speed memory PHYs across multiple technologies. As a publicly listed company on the Korean Stock Exchange Market (394280. KQ), OPENEDGES is well-positioned to continue its growth and maintain its leadership in the memory subsystem IPs market.

Learn more about the company and its offerings by visiting the official website at www.openedges.com.

About The Six Semiconductor, Inc (TSS)

TSS is a Canadian technology company and a wholly-owned subsidiary of OPENEDGES, which specializes in developing advanced high-speed DDR PHY IP solutions that cater to a wide range of applications such as AI/ML, high-performance computing (HPC), mobile devices, and automotive. The company's product portfolio includes PHY IPs for various memory standards, including LPDDR5x/5/4x/4, GDDR6, and HBM3, that are optimized for power and area. TSS's solutions are designed to be compatible with multiple technologies, foundries, and process nodes. The company's team of experts has a wealth of experience in the field and is dedicated to providing the industry with high-quality and reliable DDR PHY IP solutions. To learn more about TSS's products, visit their website at www.thesixsemi.com.

Related Semiconductor IP

- Simulation VIP for HBM3

- TSMC CLN7FF HBM3 PHY

- HBM3 Synthesizable Transactor

- HBM3 Memory Model

- HBM3 DFI Verification IP

Related News

- OPENEDGES Advances Commercialization of LPDDR6/5X Memory Subsystem IP, Targeting Next-Generation AI and HPC Markets

- DDR5/DDR4/LPDDR5 Combo PHY IP Cores which is Silicon Proven in 12FFC with Matching Controller IP Cores is available for license to accelerate your Memory Interfacing Speeds

- OPENEDGES' LPDDR5 Memory Subsystem IP Licensed by Aisin for Automotive Application

- OPENEDGES' 12nm LPDDR5/4 Memory Subsystem IP that Drives Innovation Licensed by ASICLAND

Latest News

- Arasan Announces immediate availability of its UFS 5.0 Host controller IP

- Bolt Graphics Completes Tape-Out of Test Chip for Its High-Performance Zeus GPU, A Major Milestone in Reducing Computing Costs By 17x

- NEO Semiconductor Demonstrates 3D X-DRAM Proof-of-Concept, Secures Strategic Investment to Advance AI Memory

- M31 Collaborates with TSMC to Achieve Tapeout of eUSB2V2 on N2P Process, Advancing Design IP Ecosystem

- Menta’s eFPGA Technology Adopted by AIST for Cryptography and Hardware Security Programs