Digital Blocks DB9000 TFT LCD and OLED Display Controller & Processor IP Application Leadership Advancements

Digital Blocks DB9000 Display Controller & Processor IP Core Family Extends Leadership Across Medical, Industrial, Aerospace, Automotive, Communications, Computer, Monitor, Consumer, IoT, AR/VR Headsets, Wearables, Signage, and Cinema Applications

GLEN ROCK, New Jersey, November 09, 2021 – Digital Blocks, a leading developer of silicon-proven semiconductor Intellectually Property (IP) soft cores for system-on-chip (SoC) ASIC, ASSP, & FPGA developers with display controller, 2D graphics, or video processing requirements, extends the leadership of the DB9000 Display Controller & Processor IP Core Family across a wide range of applications.

The DB9000 Display Controller & Processor IP is offered with a customer-specific range of features, supporting basic display applications. Advanced releases add optional features, such as support for multiple graphics or video layers, video up-sampling, composition, compressed frame buffer, color space conversion, hardware cursor, and high dynamic range (HDR).

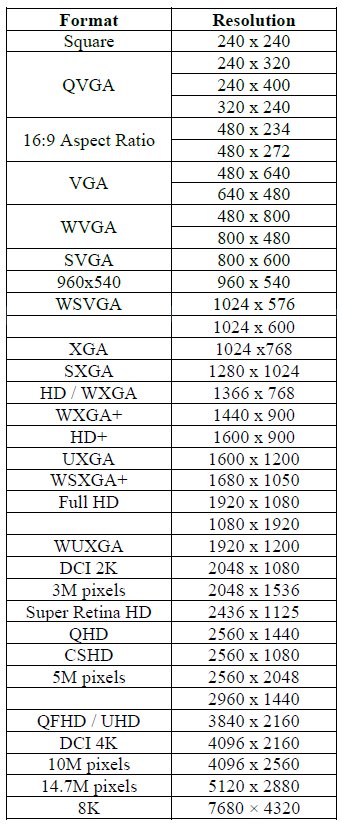

The DB9000 Display Controller & Processor IP Core supports LCD and OLED panel resolutions from 240×240 up to 8192×8192, with 1,2,4,8,16,18,24,30,32, and 36-bit bits-per-pixel, both RGB and YCrCb color spaces, with interfaces to 1, 2, 4, & 8 port LVDS, MIPI DSI, DVI, HDMI, V-by-One, and DisplayPort.

The DB9000 IP Core supports SoC fabrics interfacing to DDRn DRAM frame buffer memory with memory controller 32-, 64-, 128-, or 256-bit data widths, supporting AXI4, AXI3, AHB, AHB-Lite and Avalon protocols. With respect to the AXI protocol, the DB9000 supports multiple outstanding memory requests, supporting higher resolution panels.

Support for high resolution LCD and OLED panels includes Full High Definition (FHD), Ultra HD (UHD/Quad FHD), Digital Cinema Systems (DCI) 2K & 4K images, and 8K 7680×4320. A representative listing follows:

Price and Availability

The DB9000 Display Controller & Processor IP Core family is available in synthesizable Verilog, along with a comprehensive simulation test suite, datasheet, and user manual. For further information, product evaluation, or pricing, please go to Digital Blocks at http://www.digitalblocks.com/ip-cores/tft-lcd-display-controller-verilog-ip-core.html

About Digital Blocks

Digital Blocks is a leading developer of silicon-proven semiconductor Intellectually Property (IP) soft cores for system-on-chip (SoC) ASIC, ASSP, & FPGA developers requiring best-in-class IP for Embedded Processors, I2C/SPI/DMA Peripherals, TFT LCD/OLED Display Controllers & Processors, 2D Graphics Hardware Accelerator Engines, LVDS Display Link Layer Drivers, Video Signal & Image Processing, and Low-Latency TCP/UDP/RTP Hardware Protocol Stacks.

Digital Blocks designs silicon-proven IP cores for technology systems companies, reducing customer’s development costs and significantly improving their time-to-volume goals. Digital Blocks is located at 587 Rock Rd, Glen Rock, NJ 07452 (USA). Phone: +1-201-251-1281; Fax: +1- 702-552-1905; Media Contact: info@digitalblocks.com; Sales Inquiries: info@digitalblock.com; On the Web at www.digitalblocks.com

Related Semiconductor IP

- Display Controller

- LCD Display controller

- Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- Display Controller – LCD / OLED Panels (Avalon Bus)

- Display Controller IP

Related News

- Digital Blocks DB9000 TFT LCD and OLED Display Controller & Processor IP Application Leadership Advancements

- Digital Blocks DB9000 Display Controller IP Core Family Extends Leadership in 8K, Automotive, Medical, Aerospace, and Industrial SoC Designs

- Digital Blocks DB9000 TFT LCD Display Controller IP Core Family Achieves Leadership Across Medical, Industrial, Aerospace, Automotive, Communications, Computer, Monitor, Consumer, IoT, Wearables, and Cinema Applications

- Digital Blocks Extends the DB9000 TFT LCD Controller IP Core Family with the availability of the DB9000AHB for the AMBA 2.0 Interconnect

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard