CAST Introduces GZIP Accelerator Through New Intel FPGA Data Center Acceleration Ecosystem

WOODCLIFF LAKE, NJ USA -- October 17 2017 --A hardware accelerator that addresses the data compression and storage optimization needs of performance-critical data center applications is now available from semiconductor intellectual property provider CAST, Inc. This GZIP Accelerator Function is part of the expanded Intel® FPGA Design Solutions Network (DSN), of which CAST is an early member.

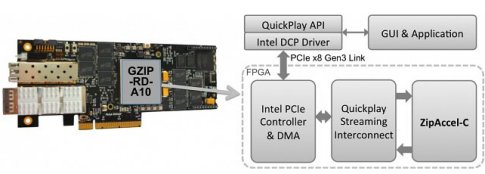

The CAST GZIP Accelerator integrates the popular ZipAccel-C™ GZIP/ZLIB/Deflate Compression IP Core with a PCIe interface, Direct Memory Access (DMA) function, and essential driver software in a high-performance, plug-and-play FPGA data compression system. Lossless data compression rates can exceed 40 Gbps, making the GIP Accelerator an excellent choice for servers or database applications, where its data compression optimizes storage requirements or reduces network bandwidth needs.

The CAST GZIP Accelerator (GZIP-RD-A10) IP implemented in an FPGA on the

Intel Programmable Acceleration Card (PAC).

The CAST GZIP Accelerator is now available as a ‘drop-in’ accelerator function for the Intel Programmable Acceleration Card (Intel PAC) with Intel Arria 10 GX FPGA that is then added to servers. The Intel PAC card also pulls in frameworks and libraries using the Intel Acceleration Stack for Intel Xeon CPU with FPGAs, easing the use of FPGA acceleration.

“We’re seeing strong demand for our hardware GZIP data compression solution from data centers and other data-heavy or performance-critical applications,” said Nikos Zervas, chief executive officer for CAST. “Running this industry-leading GZIP accelerator on the Intel PAC with the Intel Acceleration Stack provides a significant win for customers needing faster data compression and decompression.”

“Intel is collaborating with a growing ecosystem of partners in our DSN program to bring new data center accelerator functions such as CAST’s GZIP data compression to our customers seeking options to accelerate workloads,” said Reynette Au, vice president of marketing, Intel Programmable Solutions Group. “Customers and end users can benefit with faster time to market by using IP from CAST and the larger ecosystem built around our Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA.”

The CAST GZIP Accelerator is available now from CAST (www.cast-inc.com). Learn more about the accelerator function or the Intel FPGA DSN program at www.altera.com/dsn.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

Related News

- CAST and PLDA GROUP Demonstrate x86-Compliant High Compression Ratio GZIP Acceleration on FPGA, Accessible to non-FPGA Experts Using the QuickPlay Software Defined FPGA Development Tool

- OVH and Accelize Demonstrate the Value of FPGAs in the Cloud with GZIP Compression, from CAST, Achieving Acceleration Factors of >100x

- Kalray and Arm to collaborate to bring data intensive processing and AI acceleration DPU solutions to the global Arm ecosystem

- Achronix Releases Groundbreaking Speedster AC7t800 Mid-Range FPGA, Driving Innovation in AI/ML, 5G/6G and Data Center Applications

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud