Arasan Announces availability of its Total UFS 3.0 IP Solution for Xilinx FPGA's

Arasan Chip Systems, a member of the Xilinx Alliance Partner Program today announced the immediate availability of its Total UFS 3.0 IP Solution for Xilinx FPGA’s

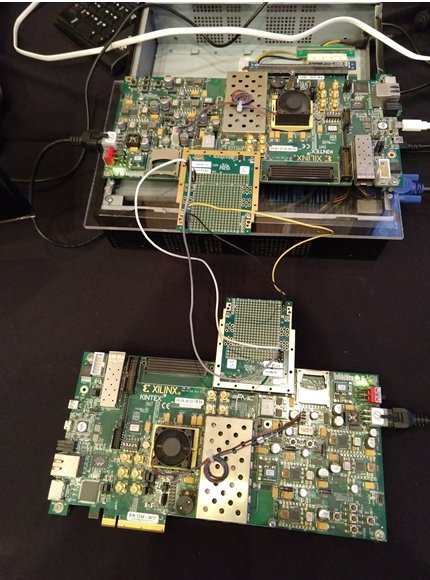

Jan 15, 2019 -- San Jose, CA --Arasan today announced the immediate availability of its Total MIPI UFS 3.0 IP Solution for use with Xilinx FPGA’s. The Arasan UFS 3.0 Master IP and UFS 3.0 Device IP compliant to the JEDEC UFS 3.0 Specification have been prototyped on Xilinx FPGA’s. Arasan uses the built in Xilinx High Speed Serdes PHY to implement the M-PHY v4.1 Gear 4 IP thereby achieving the full speed of 11.6 Gbps required by the MIPI M-PHY 4.1 Specifications. FPGA Customers can license this MIPI M-PHY v4.1 Gear 4 Digital Front End (“DFE”) IP along with our UFS 3.0 IP solution.

Arasan also sells its UFS 3.0 Prototyping Platform as a UFS 3.0 Hardware Development Kit (“HDK”) bundled in with it proprietary UFS 3.0 Software Stack. Arasan’s UFS 3.0 HDK is used by most of the UFS Compliance and production tester companies as the base platform on which their test solutions are built.

Arasan’s UFS 3.0 HDK joins the growing list of Arasan IP, including its UFS 2.1 IP, SD Card / SDIO Card IP, MIPI CSI, DSI, D-PHY and C-PHY IP that have been used in compliance and production testers. We are Compliance!

“The announcement of our UFS 3.0 IP solution for Xilinx FPGA’s furthers our alliance partnership with Xilinx and broadens our IP portfolio offering for Xilinx customers” said Prakash Kamath CTO at Arasan.

Arasan UFS IP Cores are primarily licensed by UFS 3.0 Memory Device manufacturers of which Arasan has licensed to 3 of the top 4 memory companies and Application Processor manufacturers for high end smartphone and automobiles. Arasan also works closely with Memory Device, SoC and Tester vendors to further the UFS Ecosystem and adoption.

Availability

Arasan UFS 3.0 Host IP, UFS 3.0 Device IP, UFS 3.0 Software Stack and MIPI M-PHY v4.1 DFE IP are listed on the Xilinx Alliance Website and available to license immediately. Customers who wish to migrate to ASIC can also licensed our M-PHY v4.1 IP on foundry nodes 28nm and below. The UFS 3.0 Host and Device HDK can be ordered with a moq of 6 units with a 4-6 week lead time.

About Arasan

Arasan Chip Systems, a leading provider of IP for mobile storage and mobile connectivity interfaces is an active member of the UFS Association since its inception in 2010. Arasan’s high-quality, silicon-proven, Total IP Solutions include Digital IP, Analog Mixed Signal PHY IP, Verification IP, HDK and Software. Arasan has a focused product portfolio targeting mobile SoC’s. The term Mobile has evolved over our two decade history to include all things mobile – starting with PDA’s in the mid 90’s to Smartphones & Tablets of the 2000’s to today’s Automobiles, Drones and IoT’s. Arasan is at the forefront of this evolution of “Mobile” with its standards-based IP at the heart of Mobile SoC’s.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

Related News

- Arasan and Xilinx announce their design win in providing a Total UFS 3.0 Solution to Wuhan Jingce

- Arasan Announces IP solutions for the Next Generation of Mobile Storage - UFS 3.0

- Arasan completes its Total IP Solution for the UFS 3.0 Standard with immediate availability of its MIPI M-PHY 4.1 IP Core

- Arasan Celebrates Leadership In UFS Based Storage With A Samsung Galaxy S6 Giveaway

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud