Multi-format video decoder IP Core

Hantro VC9000NanoD is a multi-format video decoder supporting all significant video standards and proprietary video formats.

Overview

Hantro VC9000NanoD is a multi-format video decoder supporting all significant video standards and proprietary video formats. It is the first HW IP decoder to support VP8 for Google’s WebM and WebRTC. Hantro VC9000NanoD was designed for battery operated devices using state-of–the-art power saving methods leading to unbeatable power consumption.

Key features

- All algorithms in HW – minimal CPU load

- Minimal power consumption – two-level clock gating

- Integrated image/post-processing block

- Extensive resolution, format and feature configurations

- HW sharing for multi-instance support

- High latency and non-sequential access delay resilience

- Feature fusing for manufacturing different chip variations

- Video and Still Image Format Support

- H.264 Baseline, Main and High Profiles, levels 1 – 5.1

- H.264 SVC Scalable Baseline and High Profiles, Base Layer only

- H.264 MVC Stereo High Profile

- MPEG-4 Simple Profile (levels 0-6) and ASP (level 0–5)

- Sorenson Spark and H.263 Profile 0, levels 10 – 70

- WMV9 / VC-1 Simple, Main and Advanced Profile, levels 0-3

- MPEG-1&2 Main Profile, levels low, med and high

- RealVideo 8/9/10

- DivX® 3/4/5/6 support – Home Theatre Profile Qualification

- VP8, VP7 and VP6

- AVS Jizhun Profile

- WebP up to 256 Mpixel

- JPEG, all common sampling formats , up to 256 Mpixel

- Target CPU

- Any ARM or similar core (CPU load is extremely low, e.g. less than 1 MHz on ARM9)

- Bus Interface Support

- AMBA AHB, AXI, AMBA 3 APB

- Configurations

- Get the optimal solution for every target application by cutting unnecessary formats and scaling the internal memories for the target resolution

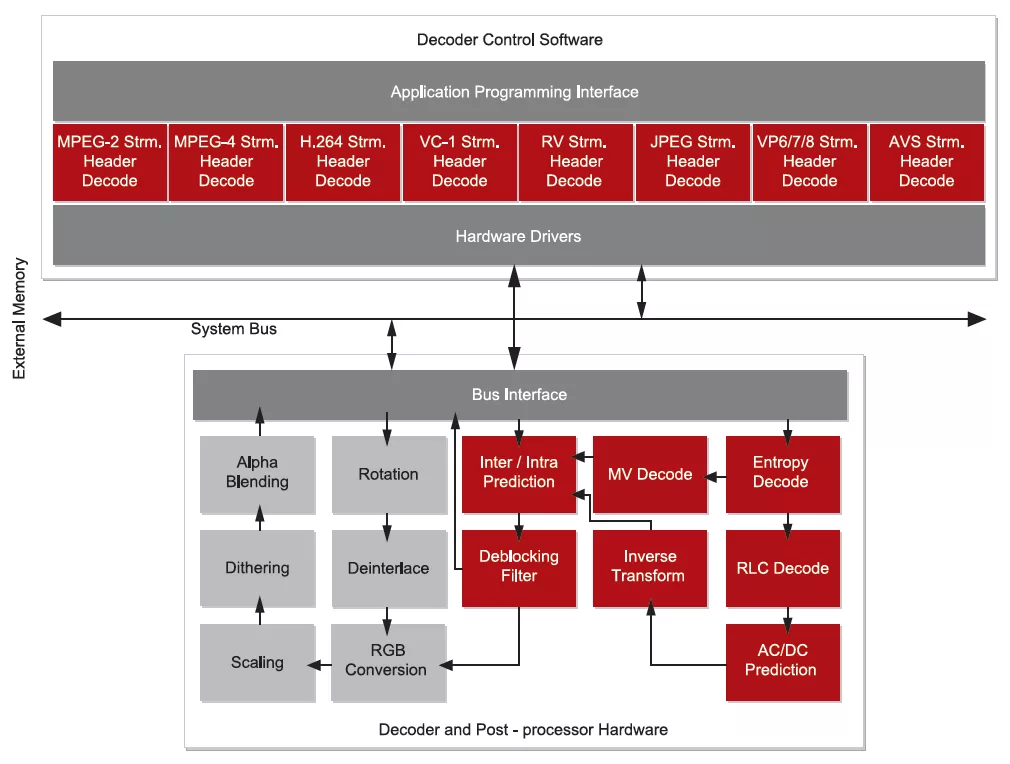

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is Multi-format video decoder IP Core?

Multi-format video decoder IP Core is a Video Processing IP core from VeriSilicon Microelectronics (Shanghai) Co., Ltd. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.