SPI (Serial Peripheral Interface) Assertion IP

SPI (Serial Peripheral Interface) Assertion IP provides an efficient and smart way to verify the SPI designs quickly without a te…

Overview

SPI (Serial Peripheral Interface) Assertion IP provides an efficient and smart way to verify the SPI designs quickly without a testbench. The SmartDV's SPI Assertion IP is fully compliant with standard SPI Specification and provides the following features.

SPI (Serial Peripheral Interface) Assertion IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SPI (Serial Peripheral Interface) Assertion IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Specification Compliance

- Follows SPI specification as defined in SPI Block Guide 4.01.

- Supports SQI interface specification and common flash device models

- Supports data width from 4 bits to 64 bits.

- Support Master and Slave Mode

- Supports 3-wire ,4-wire SPI interface

- Supports bus width 1 bit and 4 bit

- Slave device supported for SPI 3 wire are

- BOSCH SMB380

- RICOH R2033K

- Support baud rate selection

- Support internal clock division check.

- Support clock polarity (CPOL) selections.

- Support clock phase (CPHA) selection.

- Support single and burst transfer mode.

- Detects and reports the following errors.

- Mode Fault error

- In standard model mode, Mater/Slave support different types of devices. Like FLASH, EEPROM,FRAM,RTC,SQI,MOTOROLA MODE, NS MODE, TI MODE(PRECEDE and COINCIDE), EMPSPI, MACRONIX, DBI TYPE C and serial flash

- Supports single,dual and quad mode bus width operation

- Supports spansion DDR model

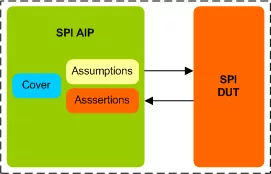

- Assertion IP features

- Assertion IP includes:

- System Verilog assertions

- System Verilog assumptions

- System Verilog cover properties

- Synthesizable Verilog Auxiliary code

- Support Master mode, Slave mode, Monitor mode and Constraint mode.

- Supports Simulation mode (stimulus from SmartDV SPI VIP) and Formal mode (stimulus from Formal tool).

- Rich set of parameters to configure SPI Assertion IP functionality.

Block Diagram

Benefits

- Runs in every major formal and simulation environment.

What’s Included?

- Detailed documentation of Assertion IP usage.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is SPI (Serial Peripheral Interface) Assertion IP?

SPI (Serial Peripheral Interface) Assertion IP is a SPI / QSPI XSPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.