QSPI Master IP

The QSPI master core is easy to use, simple to work with, quick to operate, and reliable under all conditions.

Overview

The QSPI master core is easy to use, simple to work with, quick to operate, and reliable under all conditions. It supports the majority of QSPI devices standard from a standard AXI4 slave interface. It also features support for Octal SPI, Dual SPI (DSPI), and SPI interface. The core is designed so that a user design may immediately access memory from the QSPI device in SPI mode, or alternatively issue a command to switch to any other mode. Additionally, a DMA command may be issued to copy memory from the QSPI device to anywhere else on the bus.

Key features

- Compliant with AMBA AXI3/4 and AXI4-lite protocols. An APB control port interface is available if desired instead of the AXI4-lite control port interface.

- User configurable clock frequency support

- Designed to support all leading NOR FLASH devices.

- Configurable bus width, Full & Narrow AXI burst support

- DMA for maximum bus throughput

- Supports 24 or 32b addressing and User selectable commands.

- Supports Execute in Place flash access protocols

- Backwards compatible with SPI and Dual SPI devices

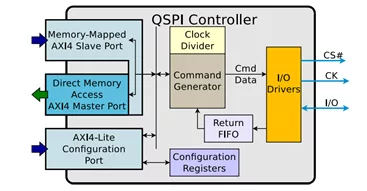

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is QSPI Master IP?

QSPI Master IP is a SPI / QSPI XSPI IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.