Interlaken Verification IP

The Interlaken Verification IP is compliant with 1.2 specifications and verifies Interlaken interfaces of designs Interlaken Inte…

Overview

The Interlaken Verification IP is compliant with 1.2 specifications and verifies Interlaken interfaces of designs Interlaken Interface. It can work with SystemVerilog,Vera, SystemC, E and Verilog HDL environment. Interlaken Verification IP is developed by experts in networking, who have developed networking products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a networking product.

Interlaken Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

Interlaken Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Implemented natively in OpenVera, Verilog, SystemC, Specman E and SystemVerilog.

- Follows Interlaken specification as defined in Interlaken protocol definition v1.2.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify env.

- Compliant to Interlaken protocol specification v1.2

- Compliant to Interlaken look aside protocol 1.1

- Compliant to Interlaken retransmission extension specification 1.2

- Compliant to Interlaken Reed-Solomon Forward Error Correction Extension 1.1

- Compliant to Interlaken Interoperability Recommendations 1.11

- Compliant to Interlaken Dual Calendar Extension 1.0

- Supports multi-channel implementation as per the specification.

- Supports configurable number of serial lanes as per the specification.

- Supports configurable burst max and burst short sizes.

- Supports insertion of extra idle to guarantee the avoidance of burst short.

- Supports scheduling calendar logic in the transmitter to choose the order in which the channels are serviced.

- Supports optional scheduling enhancement to avoid unused bandwidth by using decision algorithm.

- Each burst of transmitting data is encapsulated with burst control words before and after the data.

- Supports configurable metaframe length.

- Support configurable number of lanes from 1 to 64 lanes.

- Supports per channel inband and out of band flow control or both.

- Per-lane CRC-32 insertion into diagnostic words.

- Per lane skew insertion to test lane alignment.

- Configurable control to enable or disable the scrambler.

- 64B/67B encoding with inversion bits controllable.

- Variable test pattern generation as per specification.

- Supports test pattern generation and checking

- Supports PRBS31.

- Supports PRBS23.

- Supports PRBS7.

- Supports User defined pattern

- Supports very flexible way to test sync and alignment for state machines at startup.

- Following error injection is supported

- Receive SerDes loses lock.

- Receive logic loses word boundary sync.

- Bad scrambler state.

- Lane alignment failure.

- Burst CRC24 Errors.

- Flow Control Errors.

- Unknown Control Word Types.

- Bad 64B/67B Code words.

- Diagnostic CRC32 Errors.

- All types of CRC error injection.

- Invalid coding for all control words.

- Error injection in metaframes.

- Short burst error injection.

- Invalid burst boundary.

- Test pattern error injection.

- Comes with Interlaken Tx BFM, Interlaken Rx BFM, and Interlaken Monitor.

- Supports Interlaken interop recommendations 1.3 and 1.4.

- Rich set of configuration parameters to control Interlaken functionality.

- Supports 67 bit bus per lane or 1 bit serial lane to ease the debugging.

- Supports 80,64,40,32, 20,16,10 and 8 bit per lane serdes interface

- On-the-fly protocol and data checking.

- Notifies the testbench of significant events such as transactions, warnings,timing and protocol violations.

- Complete functional coverage for both normal and error cases.

- Callbacks in Transmit, receiver and monitor for various events.

- Status counters for various events on bus.

- Interlaken Verification IP comes with complete testsuite to test every feature of Interlaken protocol specification.

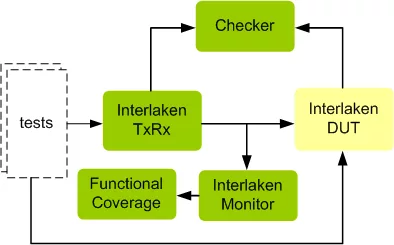

Block Diagram

Benefits

- Faster testbench development and more complete verification of Interlaken designs

- Easy to use command interface simplifies testbench control and configuration of Interlaken TX and RX

- Simplifies results analysis

- Runs in every major simulation environment

What’s Included?

- Complete regression suite containing all the testcases.

- Examples showing how to connect various components, and usage of TXRX BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Interlaken IP core

Why Interlaken is a great choice for architecting chip to chip communications in AI chips

Interlaken: the ideal high-speed chip-to-chip interface

How to design an Interlaken to SPI-4.2 bridge

The Benefits of a Multi-Protocol PMA

Multi-Channel Multi-Rate (MCMR) Forward Error Correction (FEC) - IP for High Speed Networking Applications

Frequently asked questions about Interlaken IP cores

What is Interlaken Verification IP?

Interlaken Verification IP is a Interlaken IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Interlaken?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Interlaken IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.