IDS-Verify™: From Specification to Sign-Off – Automated CSR, Hardware Software Interface and CPU-Peripheral Interface Verification

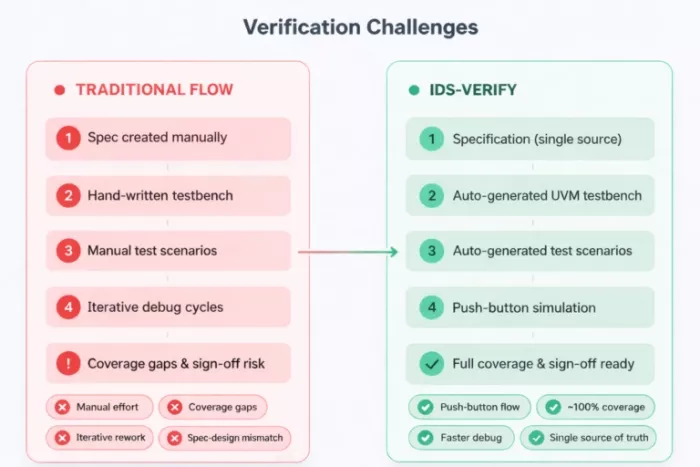

Verification of modern IP and SoC designs presents several challenges. Specifications are often interpreted differently across teams, such as design and verification, which can lead to inconsistencies in understanding the intended functionality. At the same time, achieving 100% verification coverage is difficult, as this requires significant time and multiple iterations. Maintaining homegrown scripts is also challenging, and manually writing tests and sequences can introduce errors. In addition, integrating verification components from multiple vendors further complicates the workflow. Together, these factors increase verification effort and can ultimately lead to delays in verification sign-off and tapeout.

Verification of modern IP and SoC designs presents several challenges. Specifications are often interpreted differently across teams, such as design and verification, which can lead to inconsistencies in understanding the intended functionality. At the same time, achieving 100% verification coverage is difficult, as this requires significant time and multiple iterations. Maintaining homegrown scripts is also challenging, and manually writing tests and sequences can introduce errors. In addition, integrating verification components from multiple vendors further complicates the workflow. Together, these factors increase verification effort and can ultimately lead to delays in verification sign-off and tapeout.

IDS-Verify is a tool that addresses these challenges by providing an automated verification solution. It enables automated control and status registers (CSR), CPU peripheral interface and hardware–software interface (HSI) verification by generating verification environments and tests directly from register specifications, while also producing 100% coverage reports.

A Specification-Driven Approach to Verification

IDS-Verify is a specification-driven automation solution that converts register specifications directly into executable verification environments. Users can provide register specifications in various formats, including GUI-based formats such as IDS-NG, IDS-CF, IDS-Excel, and Word, as well as standard formats such as SystemRDL and IP-XACT, along with other structured formats like XML, JSON, CSV, and YAML. From these inputs, IDS-Verify automatically generates a complete verification infrastructure, enabling a push-button verification flow from specification to sign-off. It also seamlessly integrates hand-written or third-party RTL into the generated verification environment, enabling comprehensive validation without additional manual effort.

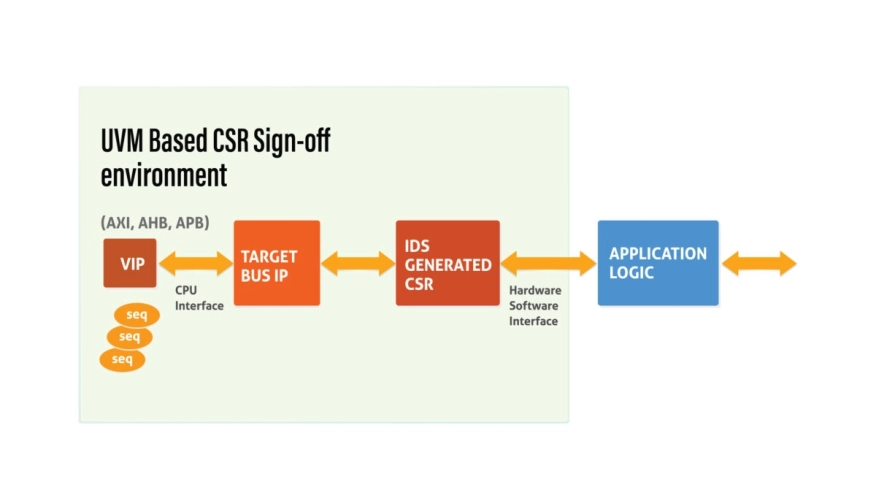

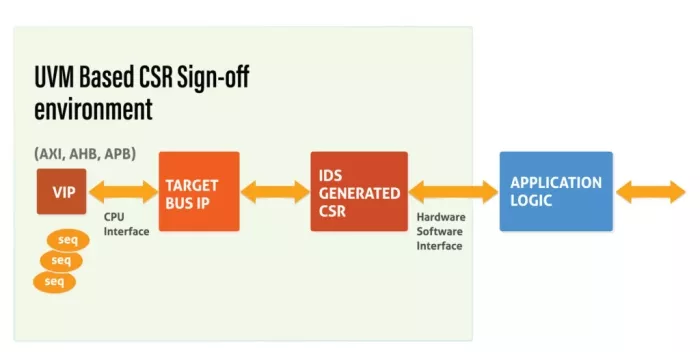

Automated CSR Verification Environment Generation

Based on the provided specification, IDS-Verify automatically generates a complete, simulation-ready CSR verification environment, eliminating the need for manual setup. It creates the entire verification infrastructure, including the UVM testbench, register model, verification sequences (both automatic and custom), functional coverage models, assertions, and bus verification infrastructure with built-in VIP. In addition, it generates all required tests and simulation-ready Makefiles compatible with industry-standard tools such as VCS®, Questa®, and Xcelium®, enabling an executable verification environment out of the box. This end-to-end automation ensures comprehensive coverage out-of-the-box, significantly reduces development effort and setup time, and enables teams to focus on higher-value verification tasks while accelerating the path to verification sign-off.

Comprehensive CSR, CPU Peripheral Interface and Hardware Software Interface Verification

IDS-Verify focuses on validating the CPU peripheral interface and Hardware Software Interface, which includes the register bank (CSR), the bus interface from CPU side and user application logic.

CPU Peripheral Interface and Bus Protocol Verification

IDS-Verify ensures that communication protocols between CPU and system components function correctly by automating bus protocol verification. It validates key aspects such as handshakes, burst behavior, transaction ordering, and timing constraints, which are critical for reliable hardware–software interaction. Traditionally, this requires developing and integrating Verification IP (VIP) and writing protocol assertions manually. IDS-Verify simplifies this process by automatically generating the required VIP, protocol checks, and test scenarios. Using this infrastructure, it executes bus transactions and verifies protocol behavior, including complex corner cases. While achieving full functional coverage of IP logic is often manageable, reaching 100% coverage for bus protocols can be challenging; IDS-Verify addresses this by providing built-in support for standard protocols such as AXI, AHB, and APB, enabling comprehensive and automated coverage of the bus interface.

CSR Verification and Automatic Test Generation

The second aspect of IDS-Verify focuses on comprehensive IP register (CSR) verification. It automatically generates tests for a wide range of register behaviors, including read/write access scenarios, reset conditions and initialization, interrupts, counters, status registers, and special registers such as alias, shadow, and lock registers. It also verifies interactions between hardware and software accesses to ensure correct functionality under all operating conditions. These automatically generated tests enable near 100% code and functional coverage, eliminating gaps commonly seen in manual verification. In addition, IDS-Verify supports user-defined custom sequences through GUI-based tools or PSS, allowing teams to extend verification for design-specific or advanced scenarios.

Coverage-Driven Sign-Off and System-Level Validation

IDS-Verify enables a coverage-driven approach to verification sign-off by providing ~100% code and functional coverage out-of-the-box. It automatically generates positive, negative, and corner-case scenarios to ensure that all coverage bins are exercised, eliminating gaps and increasing confidence in CSR and Hardware Software Interface behavior. Beyond coverage, IDS-Verify also enhances debug and system-level validation by providing clear visibility into what is working and what is failing, enabling faster root-cause analysis and reducing debug cycles. It detects integration issues early, such as missing connections or incorrect mappings, and validates CSR behavior not just in isolation but within the full context of IP, SoC, and application logic, ensuring true system-level correctness and a more reliable path to verification closure.

Key Benefits

- Specification-Driven Verification

Ensures alignment across design, verification, and software teams using a single source of truth (SSOT) - Complete Automation of Verification Flow

Automatically generates CSR UVM environments, tests, coverage, assertions, and simulation-ready Makefiles, enabling a true push-button, executable verification flow - Comprehensive CSR and HSI Coverage

Achieves ~100% code and functional coverage for CSR and hardware–software interface verification, with built-in VIP for AXI, AHB, and APB protocols - Reduced Effort and Faster Closure

Eliminates manual effort, homegrown scripts, and repetitive verification cycles, enabling faster debug, reduced iterations, and accelerated CSR sign-off - Plug-and-Play and Easy Adoption

Minimal setup required, no UVM expertise needed, and seamless integration of third-party RTL and multiple specification formats - Scalable and System-Level Ready

Scales from IP to full SoC verification, ensuring reliable CSR integration and system-level correctness - Improved Productivity and Efficiency

Frees engineers to focus on high-value verification tasks, improves team productivity, and reduces time-to-market

Conclusion

IDS-Verify™ transforms CSR,HSI, and CPU Interface verification by automating the entire flow from specification to sign-off. By generating complete verification environments, tests, and coverage models directly from specifications, it eliminates manual effort, improves consistency, and accelerates time-to-market.

Operating in the critical path of ASIC development, IDS-Verify enables teams to achieve high-confidence verification closure with minimal effort, making it an essential solution for modern IP and SoC verification.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related Blogs

- eTopus attended TSMC 2025 Symposium and showcased high-speed interface IP solutions

- Programmable Hardware Delivers 10,000X Improvement in Verification Speed over Software for Forward Error Correction

- Verification of PCIe's TDISP for Device Interface Security

- Cadence Powers AI Infra Summit '25: Memory, Interconnect, and Interface Focus

Latest Blogs

- IDS-Verify™: From Specification to Sign-Off – Automated CSR, Hardware Software Interface and CPU-Peripheral Interface Verification

- RISC-V and GPU Synergy in Practice: A Path Towards High-Performance SoCs from SpacemiT K3

- EDA AI Agents: Intelligent Automation in Semiconductor & PCB Design

- Why Security Can't Exist Without Trust

- Universal Browser Support for JPEG XL: Is Your Hardware Ready for the New Standard?