VESA DSC Decoder

The VESA DSC and VDC-M IP cores deliver visually lossless video compression for mobile, AR/VR and automotive display applications.

Overview

The VESA DSC and VDC-M IP cores deliver visually lossless video compression for mobile, AR/VR and automotive display applications.

The VESA DSC IP cores can compress any image to 8 bits per pixel (bpp), which results in a 3X compression ratio for a 24 bpp image or a 3.75X compression ratio for a 30 bpp image. The VDC-M cores use more sophisticated video encoding tools to achieve even higher compression factors for applications that require even more compression. VDC-M can reduce a 30 bpp uncompressed image to 6 bpp, and in some use cases, it can be visually lossless at a 6X compression ratio.

The VESA DSC and VDC-M IP cores can be combined with the MIPI DSI-2 Controller cores, and your choice of C/D-PHY, to form a complete display solution.

Key features

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory encoding mechanisms: MMAP, BP, MPP, and ICH

- Output buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, 12, 14, and 16 bits per video component

- YCbCr and RGB video input format

- 4:4:4, 4:2:2, and 4:2:0 native coding

- 1 pixel / clock (Encoder) and 3 pixels / clock (Decoder) internal processing architecture in 4:4:4

- 2 pixel / clock (Encoder) and 6 pixels / clock (Decoder) internal processing architecture in 4:2:2 and 4:2:0

- Parameterizable number of parallel slice encoder instances (1, 2, 4, or 8) to adapt to the capability of the technology and target display resolutions used

- Multiple slices per line in each encoder instance supported

- 100% verification coverage based on UVM environment

- Verified against the VESA DSC 1.2b C model using a comprehensive test image library

- Backward compatible with DSC 1.1

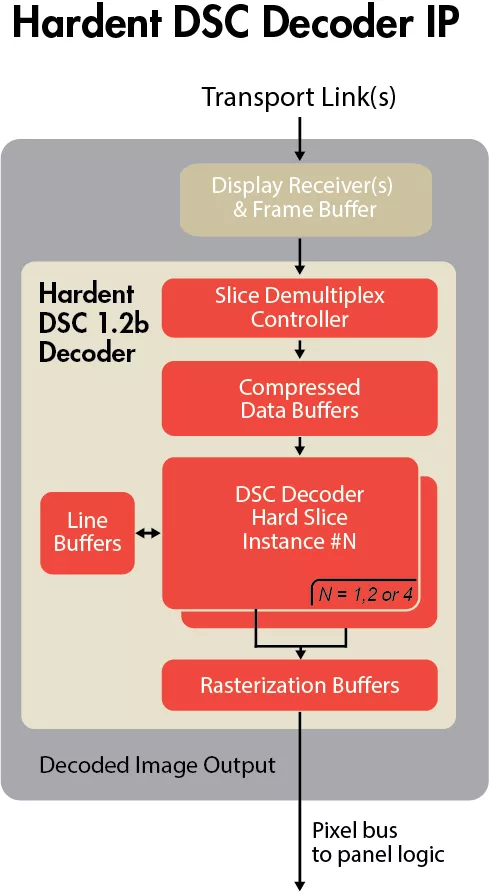

Block Diagram

Benefits

- IP customization and integration services available on request

- Multi-project licenses available

- UVM verification bindable modules

Applications

- 4K / 8K / UHD TVs

- Digital TV products

- AR / VR products

- DisplayPort 1.4 products

- HDMI 2.1 products

- USB Type-C products

What’s Included?

- Encrypted RTL source code IP core

- Functional and structural coverage reports

- Comprehensive integration guide

- Technical support and maintenance updates

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about VESA DSC IP core

VESA Video Compression on MIPI DSI-2 Enables Next-Generation Display Applications

Integrating VESA DSC and MIPI DSI in a System-on-Chip (SoC): Addressing Design Challenges and Leveraging Arasan IP Portfolio

Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

Revolutionizing Display Technology with VESA Display Stream Compression (DSC) Decoder IP

VESA Display Stream Compression (DSC) Encoder IP Core

Frequently asked questions about VESA DSC IP cores

What is VESA DSC Decoder?

VESA DSC Decoder is a VESA DSC IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this VESA DSC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this VESA DSC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.