VDC-M Decoder IIP

VDC-M DECODER core is compliant with standard VESA Display Stream Compression version 1.1/1.2.

Overview

VDC-M DECODER core is compliant with standard VESA Display Stream Compression version 1.1/1.2. Through its compatibility, it provides a simple interface to a wide range of low-cost devices. VDC-M DECODER IIP is proven in FPGA environment. The host interface of the VDC-M DECODER can be simple interface or can be AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

VDC-M Decoder IIP is supported natively in Verilog and VHDL

Key features

- Supports VDC-M specification version 1.1 and 1.2.

- Supports full VDC-M decoder functionality.

- Supports following maximum bitrates (BPPmax), as follows:

- 3 × bits_per_component,for 4:4:4

- 2 × bits_per_component,for 4:2:2

- 1.5 × bits_per_component,for 4:2:0

- Supports any integer slice per line values

- Supports any combination of bits_per_pixel and slice_width

- Supports CSC(Color-space-conversion)

- Supports the following Picture Hierarchy,

- Block Level

- Slice Level

- Picture Level

- Supports the following Per-mode Decoding Process ,

- Transform Mode

- BP Mode

- MPP Mode

- Fallback Modes

- MPPF Mode

- BP-SKIP Mode

- Supports rate control (RC) algorithm in the determination of QP

- Supports substream de-multiplexing

- Supports Syntax parsing for Transform, BP, MPP, MPPF, and BP-SKIP modes

- Supports following Hadamard transform applied in the YCoCg color space

- 8-point Forward Hadamard Transform

- 4-point Forward Hadamard Transform

- Supports PPS decoding.

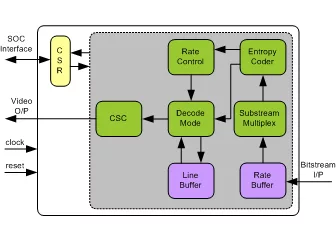

Block Diagram

Benefits

- Single site license option is provided to companies designing in a single site.

- Multi sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

What’s Included?

- The VDC-M DECODER interface is available in Source and netlist products.

- The Source product is delivered in plain text verilog.If needed VHDL,SystemC code can also be provided.

- Easy to use Verilog Test Environment with Verilog Testcases

- Lint, CDC, Synthesis, Simulation Scripts with waiver files

- IP-XACT RDL generated address map

- Firmware code and Linux driver package

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about VESA DSC IP core

MIPI: Powering the Future of Connected Devices

VESA Video Compression on MIPI DSI-2 Enables Next-Generation Display Applications

Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

Revolutionizing Display Technology with VESA Display Stream Compression (DSC) Decoder IP

VESA Display Stream Compression (DSC) Encoder IP Core

Frequently asked questions about VESA DSC IP cores

What is VDC-M Decoder IIP?

VDC-M Decoder IIP is a VESA DSC IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this VESA DSC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this VESA DSC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.