ULL PCIe DMA Controller

Unlock High-Speed Data Transfer Between SmartNICs and Host CPU The ULL PCIe DMA Controller is a high-performance, bidirectional d…

Overview

Unlock High-Speed Data Transfer Between SmartNICs and Host CPU

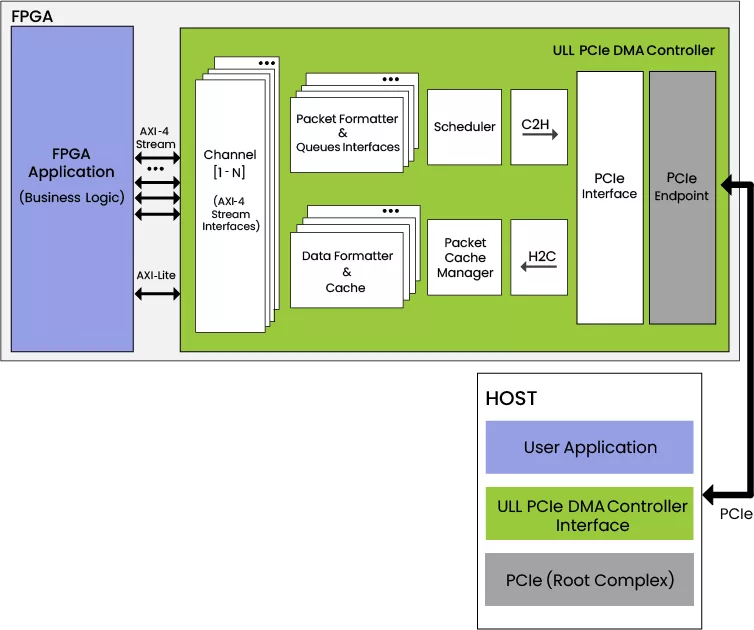

The ULL PCIe DMA Controller is a high-performance, bidirectional data transfer solution. It is designed for seamless communication between FPGAs and host CPUs over PCIe. With a round-trip time as low as 585ns*, this IP core empowers developers to maximize resource utilization and achieve ultra-low latency without compromising performance.

* RTT min latency, PCIe Gen4 x 8 lanes, Xilinx/AMD x3522pv, Intel® Core™ i9-14900KS CPU @5.90GHz, Synchronous AXI-4 Interfaces (512b, 250MHz), Payload counts: 128k

Key features

- High speed & flexibility: Obtain exceptional performance for latency-critical core applications. The ULL PCIe DMA Controller is designed using cut-through techniques to optimize latency to move data and control/status messages across the PCIe link.

- Seamless FPGA Integration: In the card-to-host direction, packets are transferred through PCIe from FPGA to host buffer memory in separate memory blocks, one or many blocks depending on the packet size. In the host-to-card path, packets are transferred directly to the FPGA memory space through optimized PCIe transactions.

- Kernel-Bypass Optimized for Linux Applications: Designed explicitly for Kernel-bypass Linux environments, our controller leverages a polling and ring buffer DMA architecture to support ultra-low latency needs in high-throughput systems.

Block Diagram

Benefits

- Scalability: Highly parametrizable IP Core (Number of channels, Number of queues per channel, Memory size of each queue, Interfaces AXI-4 Stream bus width and synchronous or asynchronous to PCIe clock)

- Easy to use: Linux kernel module provided with standard delivery packages (rpm, deb), driver created to automatically detect PCIe card for early evaluation solution, library API easily handles buffer creation, transmission and reception

- Implementation

- Highly efficient FPGA implementation with low resources utilization, and high timing margin on -2 and -3 Xilinx/AMD UltraScale+ FPGA

- Integration: Fully integrated with AMD/Xilinx PCIe Endpoint (up to Gen 4 x8), and easy integration with Orthogone TCP/IP and UDP/IP network stacks

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is ULL PCIe DMA Controller?

ULL PCIe DMA Controller is a PCI Express IP core from Orthogone Technologies inc. listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.