PCIe Gen 5 Verification IP

The PCIe Gen 5 Verification IP provides an effective & efficient way to verify the components interfacing with PCIe Gen 5 interfa…

Overview

The PCIe Gen 5 Verification IP provides an effective & efficient way to verify the components interfacing with PCIe Gen 5 interface of an IP or SoC The PCIe Gen 6 VIP is fully compliant with latest PCI Express Gen 5 specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key features

- Support for 32.0 GT/s Data Rate per lane with backwards compatible.

- Optimizing the Link to skip equalization at lower Data Rates when supporting 32.0 GT/s(optional feature).

- Lower pin count in pipe interface when supporting 32.0 GT/s.

- Support for newly added phy serdes architecture in pipe specification 5.0 .

- Support for modified TS1 & TS2 order set.

- Compliant with PCI Express Specifications 4.0 v1.0 (16GT/s), 3.0 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Verification IP configurable as PCI express Root Complex and Device Endpoint.

- Configurable LinkWidth: x1, x2, x4, x8, x12, x16, x32.

- Configurable original pipe width : 8,16,32,64 and for Serdes Architecture: 10, 20, 40, 80

- Supports Low Power management LTSSM states - L0s, L1, L2, L1 sub states,PCI- PM, ASPM.

- Advanced Error Reporting (AER) with optional Malformed TLP checks, ECRC and TLP Poisoning support.

- Compliance testing in TL, DLL & PL including power management test-suites.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks).

- Graphical analyser for all three Layers to show PCIe transactions for easy debugging.

- Complaint with Pipe specification 5.1

- Supports scale flow control and lane margining feature.

- Supports simplified replay timer and SR-IOV

- Supports 10-bit Tag as requester as well as completer.

- Support for ATS with latest ATS Specification revision 1.1.

- Supports LTR & FLR (Function Level Reset)

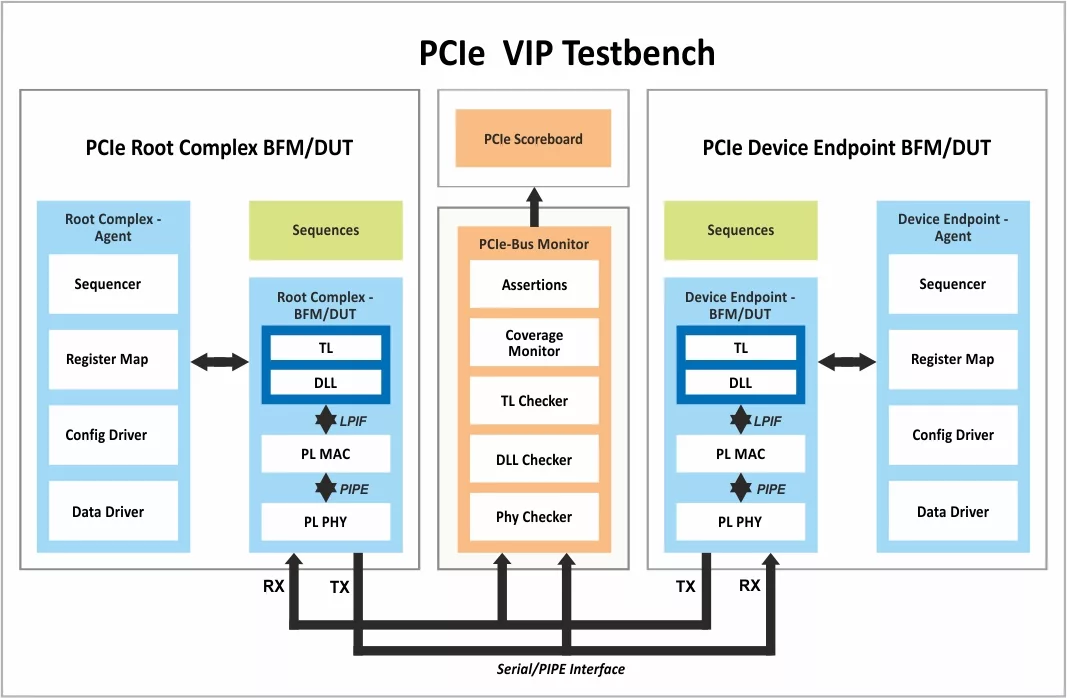

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

What’s Included?

- PCIe Gen5 Root-Complex/Device-Endpoint

- PCIe Gen5 BFM/Agents for :

- PHY Layer

- Data Link Layer

- Transaction Layer

- Register Space

- PCIe Gen5 Layered Monitor and Scoreboard

- Test Environment & Test Suite :

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Compliance Tests

- Integration Guide, User Manual and Release Notes

Specifications

Identity

Standards & Interfaces

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is PCIe Gen 5 Verification IP?

PCIe Gen 5 Verification IP is a PCI Express IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.