UFS HOST Controller IIP

UFS HOST Controller provides full support for the UFS synchronous serial interface, compatible with UFS version 3.6 specification.

Overview

UFS HOST Controller provides full support for the UFS synchronous serial interface, compatible with UFS version 3.6 specification. Through its UFS compatibility, it provides a simple interface to a wide range of low-cost devices. UFS HOST IIP is proven in FPGA environment. The host interface of the UFS can be simple interface or can be AMBA APB, AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

UFS HOST Controller IIP is supported natively in Verilog and VHDL

Key features

- Supports high performance M-PHY type-1.

- Supports full UFS Host functionality.

- Supports UFS driver layer over UniPro.

- Supports configurable cport.

- Supports Application Interface APB and AXI.

- Supports complete control of UIC Layer by UFS Host

- Supports VIP interface at MPHY Serial, MPHY RMMI and Unipro CPort level.

- Supports UFS-Specified commands of Specification JESD220C (UFS 2.1).

- Supports UFS-Specified commands of Specification JESD220D (UFS 3.0).

- Supports UFS-Specified commands of Specification JESD220E (UFS 3.1).

- Supports Unified Memory Extension JESD220-1A (Version 1.1).

- All UPIU Processing

- - Datain, Dataout, Command, Response, RTT, Query, Task Management and Reject.

- Supports various UFS layers

- - UFS Command Set Layer (UCS)

- - UFS Transport Protocol Layer (UTP)

- - UFS Interconnect Layer (UIC).

- Includes MIPI UniPro and M-PHY VIP for UFS Interconnect Layer verification

- - MIPI UniPro is adopted for data link layer

- - MIPI M-PHY is adopted for physical layer

- - Proven MIPI UniPro BFM

- - Proven MIPI M-PHY BFM

- - Supports up to 2-lanes (restricted by Standard) running at HS-G4 (10Gbps).

- - All PWM gears support.

- - All HS gears support

- - Enter hibernate and exit hibernate supported

- - Complex LSS feature verification support to cover all cases, Like lane mapping, reverse lane mapping, errors in UPR sequences etc

- - All DME commands supported

- - Low power with multiple power operating mode

- - Various types of error injection at UniPro and MPHY layers

- - L1.5 and C port test mode features supported

- - Advanced L1.5, L2 and C port error injection

- - All L2 Preemption and error cases supported

- - Supports Unipro 1.41, Unipro 1.6 , Unipro 1.8 specifications

- - Support MIPI MPHY specification 3.0 ,4.1 specifications

- - Low power with multiple power operating modes.

- - Supports RMMI bus width for 10,20,40 bits per lane

- - Supports MIPI MPHY 3.0, MIPI MPHY 4.1 specifications

- - Low power with multiple power operating modes

- Supports boot mode operation.

- Supports device enumeration and discovery.

- Priority arbitration between command, query and task management UPIUs and indexed based processing within Command and Query UPIUs.

- Supports 32 UTP Transfer request descriptors and 8 UTP Task Management Descriptors for UFS host.

- Supports multiple partitions (LUNs) with partition Management.

- Supports Multiple User Data Partition with Enhanced User Data Area options.

- Supports for boot partitions and RPMB partition.

- Supports for Reliable write operation.

- Supports for Background operations.

- Supports for Secure operations, Purge and Erase to enhance data security.

- Supports for Write Protection options, including Permanent & Power-On Write Protection.

- Supports for Signed access to a Replay Protected Memory Block.

- Supports for HW Reset Signals.

- Supports Task management operations.

- Supports Power management operations.

- Supports automatic/user tag generation.

- Supports all Initiator ID values.

- Supports UFS HCI as per the specification JESD223C.

- Supports Priority LUN handling.

- Supports below latest UFS Version 3.1 features

- - UFS-Deep Sleep Power Mode

- - Performance Throttling Event Notification

- - Write Booster

- Supports HPB version 1.0 and 2.0 as per latest spec

- Error injection and detection in all levels of UFS protocol.

- Notifies the testbench of significant events such as transactions, warnings,timing and protocol violations.

- Supports constraints Randomization.

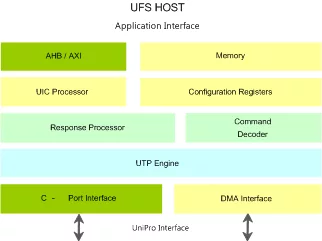

Block Diagram

Benefits

- Single site license option is provided to companies designing in a single site.

- Multi sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs,license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

What’s Included?

- The UFS interface is available in Source and netlist products.

- The Source product is delivered in plain text verilog or VHDL or SystemC source code.

- Integration test-bench and tests.

- Scripts for simulation and synthesis with support for common EDA tools.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UFS Controller IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

UFS or NVMe in Smartphone? See Apple's answer!

UFS Goes Mainstream

eMMC: The Embedded Storage Powering On-Device AI

Frequently asked questions about UFS Controller IP

What is UFS HOST Controller IIP?

UFS HOST Controller IIP is a UFS Controller IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.