UFS 2.1 Stack & Driver

The UFS 2.1 Host Stack is a stack developed for UFS Host Controllers that are used to connect to UFS devices via UniPro/M-PHY.

Overview

The UFS 2.1 Host Stack is a stack developed for UFS Host Controllers that are used to connect to UFS devices via UniPro/M-PHY. The stack can also be used for validating a UFS device during its development and integration life cycles thereby helping designers to reduce the time to market for their product.

The modular UFS 2.1 Host Stack is architected to be OS and platform independent which eases porting effort. It has thin OS and hardware abstraction layers making it highly portable.

The UFS 2.1 Host Stack has a low-level hardware layer that is purely OS independent and users can use this layer alone for UFS host/device validation with no driver complexity. The UFS stack provides a generic API set to access, control, and configure the bus driver, host controller driver, and the underlying hardware. The stack includes functions for UFS initialization, UniPro attributes configuration, sending/Receiving of commands/tasks in the form of UPIUs, data transfer, UFS interrupt handling, UFS device configuration, and UFS host controller hardware configuration. The UFS 2.1 Host Stack can support a single UFS host controller with a single UFS Device.

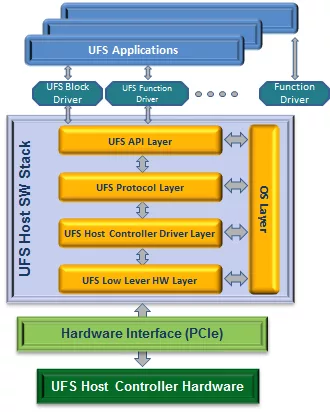

The UFS host stack consists of the following layers:

- a) Application Interface Layer (API Layer)

- b) Protocol Layer

- c) Host Controller Driver Layer

- d) Low level Hardware Abstraction Layer

- e) OS Abstraction Layer

The layered architecture allows for easy porting to various operating systems and various platforms. Client applications such as the function drivers interface with the API layer to use the UFS device. The low level details of the protocol is abstracted for the end-user and is handled in the software stack. A set of well defined APIs are provided at this layer.

Key features

- Compliant with JEDEC UFS HCI 2.0 and MIPI UniPro Specification version 1.6

- Portability in choice of OS, processors and hardware

- Easy-to-use interface for applications

- Fully documented generic device operation API

Block Diagram

Benefits

- System manufacturers can port the UFS stack to respective system hardware and operating systems

- Silicon developers can use the driver and board environment to test the device silicon during development

- Silicon vendors can use the driver to create a reference system design for their customers

What’s Included?

- Source code (in c language) and/or binaries for applicatioin processor UFS stack.

- API Guide.

- User manual.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UFS Controller IP core

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Vertically Integrated MIPI Solutions

Design & Verify Virtual Platform with reusable TLM 2.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

Frequently asked questions about UFS Controller IP

What is UFS 2.1 Stack & Driver?

UFS 2.1 Stack & Driver is a UFS Controller IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.