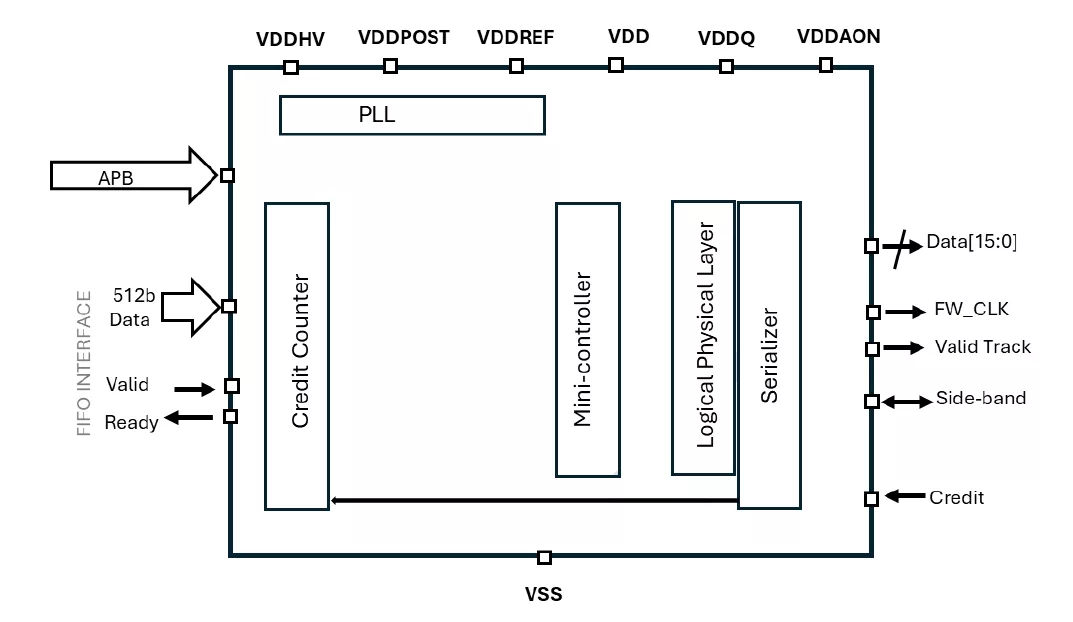

UCIe TX Interface

The ODT-UCIE-UNI-TX-16GXX-16FFCT is a low power D2D transmitter IP in TSMC 16FFC process.

Overview

The ODT-UCIE-UNI-TX-16GXX-16FFCT is a low power D2D transmitter IP in TSMC 16FFC process. With 16 lanes at 16GT/s, up to 256GT/s (32GBps) of data can be transmitted to another chip within the same package, up to 25mm.

UCIe sideband communications facilitate link bring-up and training without need for other interfaces. This unidirectional IP transmits data using Raw UCIe transport for 100% bandwidth efficiency with no retries. The interface accepts 512-bits of transmit data input.

Key features

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

- Mainband: 16GT/s per lane, 16 Tx Lanes

- < 1E-15 BER

- Sideband: 800MT/s, Tx, Rx, TxClk, RxClk

- UCIe-Standard Package support

- Channel length up to 25 mm

- Functional from -40°C to 125°C

- Bump pitch: 130 um

- 30V CDM ESD

- Beach front density: 112 Gbps/mm

- -2.2dB switchable deemphasis on Tx

- 8GHz Integer PLL

- 100MHz Internal reference clock

- Differential clock forwarding

- Link Training

- Low latency, High BW efficiency

- Statistics counters and error reporting

- Self-calibration

- Runtime recalibration

- Clock skew for training and eye monitor

- Sideband messaging for link training and parameter exchange

- Scrambling

- Loopback BIST for KGD

- APB interface for register management

Block Diagram

Applications

- D2D Connectivity for MCM applications

- Ideal process for peripherals, such as data conversion, networking, storage, radio, and sensing

- High integration for size-constrained mobile, aeronautic, and automotive systems

- High bandwidth at low power for battery- and self-powered systems

- Helps integrate massive amounts of data for signal processing and AI

- Peripheral hubs and interconnects

What’s Included?

- Datasheet

- PHY: Hard Macro (GDSII) for the PHY

- FIFO: RTL, Synthesis Scripts

- Abstract View (LEF) for top level connectivity

- System Verilog Behavioral Model

- Integration and Customer Support

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 16nm | FFC | — |

Specifications

Identity

Provider

Learn more about UCIe IP core

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is UCIe TX Interface?

UCIe TX Interface is a UCIe IP core from Omni Design Technologies, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.