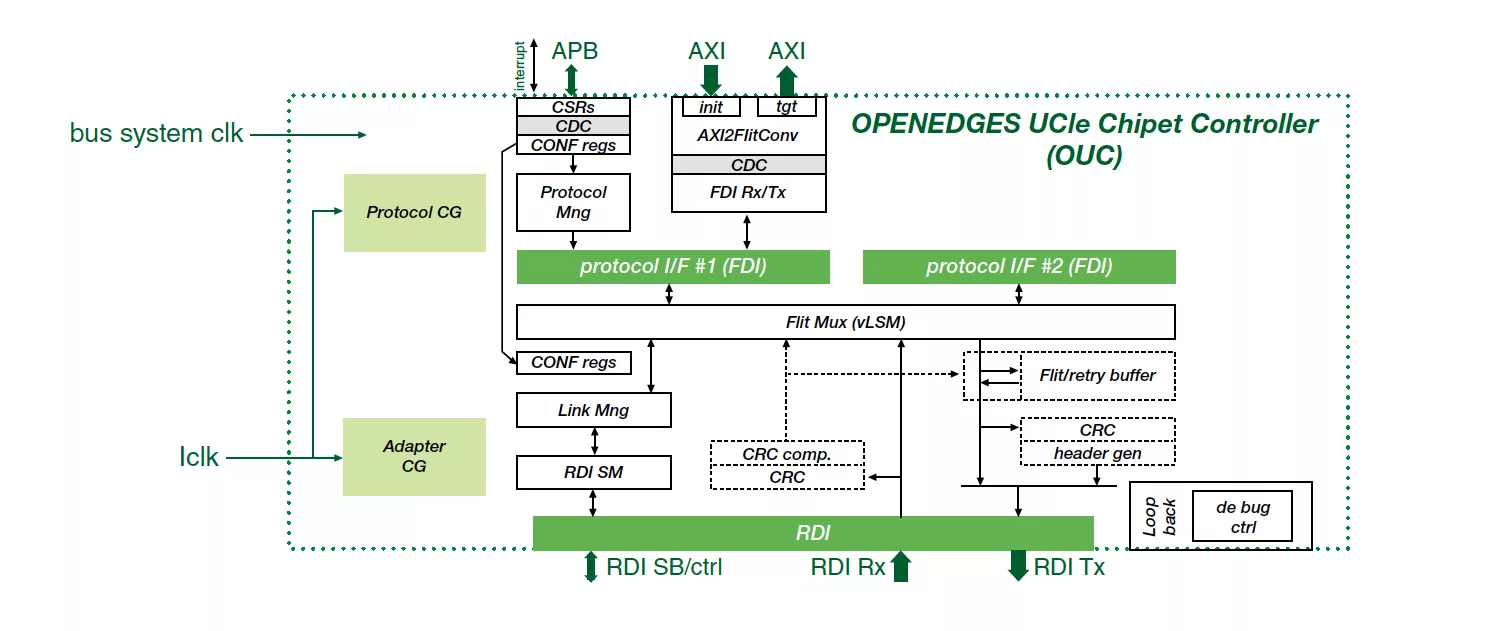

UCIe Die-to-Die Chiplet Controller

The UCIe Controller IP is a configurable and customizable UCIe 1.1 compliant die-to-die controller.

Overview

The UCIe Controller IP is a highly configurable and customizable UCIe 1.1 compliant die-to-die controller. It extends on-chip AXI interconnections to multi-die connections, providing an advanced solution for multi-die connectivity across various applications. The controller uses flits, which are flow control units that are both reliable and latency-optimized. In addition, OUC ensures that the receiver buffer does not overflow at the receiver end. With its well-defined AXI packet structure, the OUC seamlessly matches AXI parameters with its link partner, ensuring smooth format matching and communication even with different AXI parameters. OUC matches the protocol using padding and cropping with default operation rules defined in AXI.

This UCIe chiplet brings highly customizable, package-level integration with die-to-die interconnect and protocol connections, creating an interoperable, multi-vendor ecosystem, and establishing a new industry standard for universal interconnect at the package level.

Key features

- AXI over UCIe Streaming Protocol

- High configurability and customizability

- Defines packets to communicate with a link partner using different AXI parameters

- Supports raw streaming modes

- Provides various Flit formats in UCIe v1.1 (filt format 2: 68B flit format, flit format 3/4: standard 256B flit format, and flit format 5/6: latency optimized 256B flit format)

- Link Error Detection and Retry Feature

- Implements CRC and retry mechanisms

- Handles parity error effectively

- APB for Controller Control

- Manages parameter setup

- Controls link operations

- Facilitates test and debug processes

Block Diagram

Benefits

- Configurability

- AXI interface including widths and signals

- RDI/FDI data width (32byte/16byte)

- Flit format

- Address map

- Simulation Model

- Supports host bus integration

- Includes software layer for UCIe controller

- Facilitates Design Space Exploration (DSE) for UCIe switching fabric

- Enables traffic generation for performance estimation

- High Operation Frequency

- Achieves 1+GHz operating frequency on SEC 5nm automotive process

- Configured with 32B FDI/RDI data width

- Verification Environment

- Features UCIe controller loop-back environment with traffic generator and checker for on-chip validation

- Integrates UCIe Controller and PHY

Applications

- Automotive

- Ai accelerators

- AI/ML

- high computing and servers, etc

What’s Included?

- OUC is packaged with the following items to all eligible companies:

- IP core RTL

- Standalone Simulation Environment

- Management SW

- IP Documentation

Specifications

Identity

Provider

Learn more about UCIe IP core

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is UCIe Die-to-Die Chiplet Controller?

UCIe Die-to-Die Chiplet Controller is a UCIe IP core from OPENEDGES Technology, Inc. listed on Semi IP Hub.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.