TSMC CLN5FF GUCIe LP Die-to-Die PHY

IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face package.

Overview

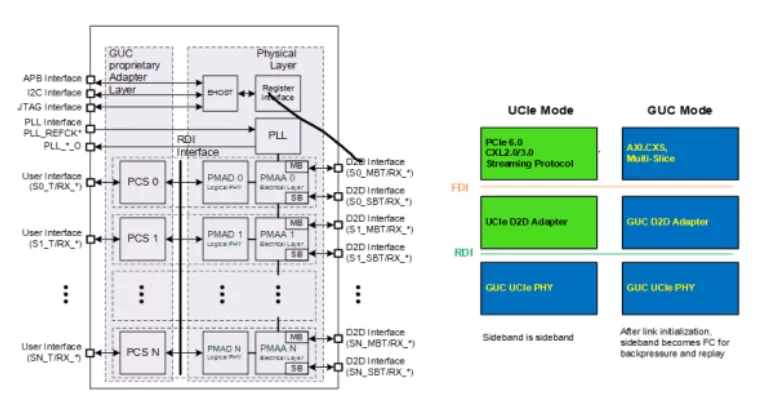

IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package. This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the GUC proprietary Physical Coding Sublayer (PCS) to provide low- latency flow control for fast linked with AXI/CXS bus and provide error data replay (PCS-replay) feature to ensure the data transferred to RX is error-free. This IP is the UCIe Advanced package compliant that transmits data through TSMC advanced packaging solution at Chip-on-Wafer-on-Substrate (CoWoS® ) with the Silicon and Redistribution Layer (RDL) interconnect interposer.

IGAD2DY11A contains 64 TX lanes and 64 RX lanes per module and supports the configurable number of modules up to eight in one PHY. Each TX/RX lane supports up to a 4/8/12/16/24/32/36 GT/s data rate. In summary, This IP offers a full-duplex data transmission with extremely low power and up to 2304 GT/s data rate per module in both directions. IGAD2DY11A contains the Electrical (Analog) Layer and Logical PHY Layer that support

serialization, deserialization, link training, eye training, lane repair, lane reversal, scrambling and descrambling, sideband initialization and transfer, and clock forwarding functions. A Phase-Locked Loop (PLL) is also included.

Technology

- Process: TSMC 5 nm 0.75 V/1.2 V CMOS LOGIC FinFET Process

- Metal scheme: 1P17M (1X_h_1Xb_v_1Xe_h_1Ya_v _1Yb_ h_5Y_vhvh_2Yy2Yx2R)

- Special layer & device: N/A

Key features

- 32 GT/s UCIe compliance

- Max speed stretch to 36 GT/s

- 64 full-duplex lanes per module

- Support CoWoS-R/S/L

- Up to 8-module Analog PHY included in the analog hard macro

- UCIe RX matched length architecture

- Lane repair for Data, Valid, and CLK

- Built-in test pattern and checker

- EHOST: APB3, I 2C, and JTAG register interface

- 1.2 V analog supply voltage for PLL/Analog PHY and 0.75 V analog/digital supply voltage

- Independent low-power mode for analog blocks

- Operating junction temperature: -40 °C ~ 125 °C

- Marco size: 3509.151 μm (width) x 1436.4 μm (height) for NS orientation

Block Diagram

Applications

- For applications with wired communications, such as AI and HPC.

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 5nm | N5FF | — |

Specifications

Identity

Provider

Learn more about UCIe IP core

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is TSMC CLN5FF GUCIe LP Die-to-Die PHY?

TSMC CLN5FF GUCIe LP Die-to-Die PHY is a UCIe IP core from Global UniChip Corp. (GUC) listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.