Overview

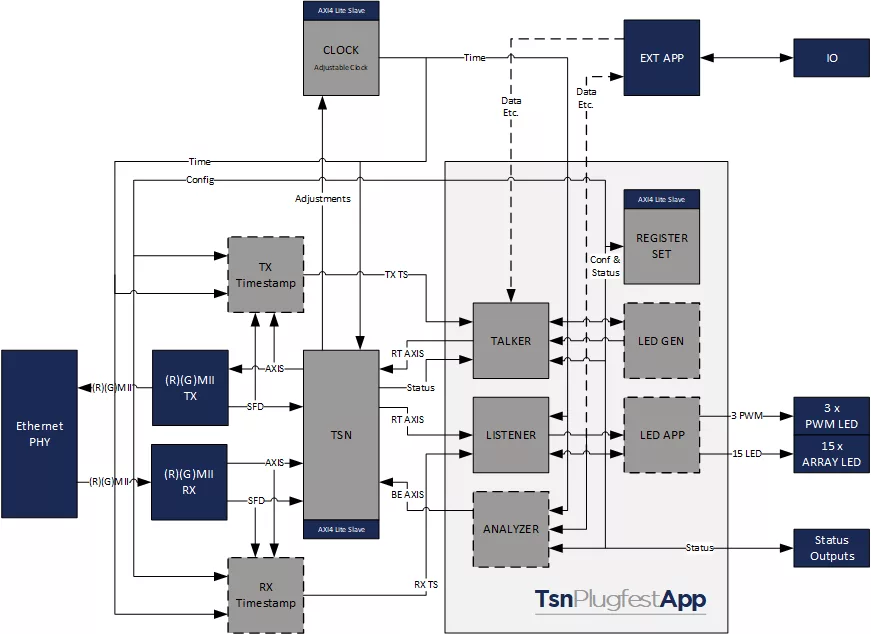

The TSN Industrial Internet Consortium(R) (IIC) Plugfest Application is a companion core for the TSN IP cores from NetTimeLogic. The IIC(R) Plugfest Application implements an OPC/UA Talker, Listener, Analyzer and Publisher according to the interoperability application used at the IIC(R) TSN Testbed, as well as the IIC(R) LED Strip Application and a LED Pattern generator. It also offers an external application interface to connect a custom application to the Plugfest Application without the need to handle frame encoding/decoding in the application or a specific timing.

The Talker will send periodically, precisely timely aligned OPC/UA frames with hardware timestamps and data encapsulation.

The Listener will parse and extract the data and meta data from the OPC/UA frames and take hardware timestamps on reception which will be used by the Analyzer and Applications.

The Analyzer and Publisher calculates statistics over the received OPC/UA frames and publishes the statistics via frames for status supervision and analysis.

The LED Application is a PWM generator for the LED brightness based on the data from the Listener according to the LED Strip Application defined by the IIC(R). It also has a LED pattern generator which is connected to the Talker as the counterpart to the LED Appliction.

The Core connects to the TSN cores via AXI stream with two differnet streams: a high priority and a best effort stream and uses the status information from the TSN core as input for the OPC/UA frames.

The core gives a fast and easy solutionto take part in the IIC(R) Testbed/Plugfests.

All tables, protocols and algorithms are implemented completely in HW in the core, no CPU is required, except for configuration. This allows running OPC/UA stream handling in hardware without an OPC/UA software stack.

Learn more about I2C / I3C IP core

The I2C (Inter-Integrated Circuit) Bus invented in 1980 by Philips Semiconductors (NXP Semiconductors today) was a massive step forward in simplifying communications in embedded systems. It is a simple two-wire interface for synchronous, multi-master/multi-slave, single ended serial communication. Fast forward 45 years to today and it is still widely used for attaching low speed peripheral Integrated Circuits (ICs), processors and microcontrollers. But silicon today has changed...

Early in my career selling chips for Motorola Semiconductor, the ability to spin derivative microcontroller chips for a customer’s specific requirement was relatively straightforward. If the volume looked reasonable, we would tape-out a new chip with a few added features because mask costs and wafers were relatively inexpensive at the larger process nodes. The customer won by getting an MCU tailored to their specific need, and Motorola won by gaining a more committed customer plus another SKU that could be sold to other customers – boosting ROI. With the migration to higher cost FinFET nodes, those times are long gone as the economics no longer work.

Sharmion Kerley, MIPI Director of Marketing and Membership

Imagine a camera subsystem that responds in microseconds, consumes less power, and offers a more straightforward route to time-to-market. For SoC architects and IP integration teams, that vision is increasingly possible with MIPI Camera Control Interface (CCI) over I3C.