MIPI I3C Target Device

Smart connectivity for mobile, IoT, and automotive innovation The DI3CS device is an I3C Target that complies with the MIPI® Alli…

Overview

Smart connectivity for mobile, IoT, and automotive innovation

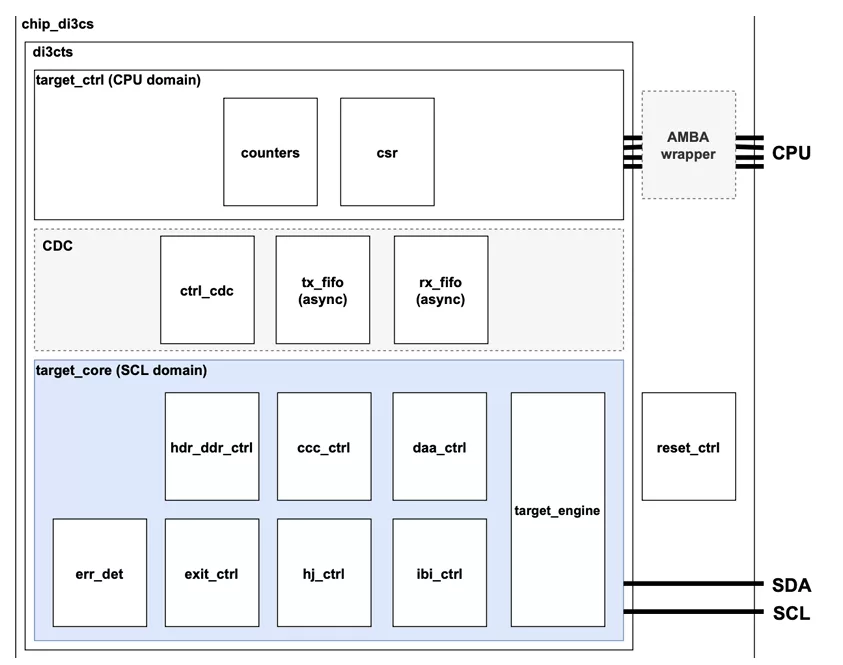

The DI3CS device is an I3C Target that complies with the MIPI® Alliance I3C Basic Specification. As an I3C Target Controller, it is a peripheral device designed to communicate with an I3C Master over the I3C bus. I3C, or Improved Inter-Integrated Circuit, provides an advanced, high-speed communication protocol that builds on I2C’s legacy while offering improvements in speed, power efficiency, and scalability.

The DI3CS device implements all the required functions defined by the I3C Basic specification and several optional features. It is designed for ease of integration and efficient operation in systems with other I3C devices. Implemented features includes handling of Single Data Rate (SDR), Double Data Rate (DDR), Dynamic Address Assignment, In-Band Interrupt (IBI) generation, Hot-Join generation, Common Command Codes execution, Error Detection and Target Reset functionality.

The DI3CS device, as an I3C Target, is designed to deliver high-speed, low-power, and reliable communication in systems that use the I3C protocol. By implementing all functions as defined in the MIPI I3C Basic Specification, DI3CS is ideal for integration into modern embedded systems, sensors, and other peripheral devices. Its support for dynamic addressing, in-band interrupts, high data rates, and backward compatibility with I2C ensures versatility and future-proof performance.

Key features

- MIPI I3C Basic Specification v1.2 compiliance

- Native 32-bit CPU Interface

- Optional CPU interface wrappers (APB, AHB, AXI)

- Legacy I2C communication with 7-bit Static Address

- I3C Single Data Rate (SDR) mode

- Double Data Rate (DDR) suport

- Dynamic Adress Assigment (DAA) supprot

- Common Command Codes (CCC) execution

- In-Band Interrupts (IBI) suport

- Hot-Join (HJ) support

- Target Reset mechanism supprot

- TE0-TE6 Errors detection and recovery (SDR)

- Frame, parity, CRC, data errors detection and recovery (DDR)

- Configurable Asynchronous RX FIFO

- Configurable Asynchronous TX FIFO

- Masked interrupts

Block Diagram

What’s Included?

- HDL Source Code

- Testbench environment

- Automatic Simulation macros

- Tests with reference responses

- Synthesis scripts

- Technical documentation

- 12 months of technical support

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is MIPI I3C Target Device?

MIPI I3C Target Device is a I2C / I3C IP core from Digital Core Design listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.