Static RAM Controller

The SRAM-CTRL implements a Static Random Access Memory (SRAM) Controller translating AHB, or AXI4, or APB bus reads and writes in…

Overview

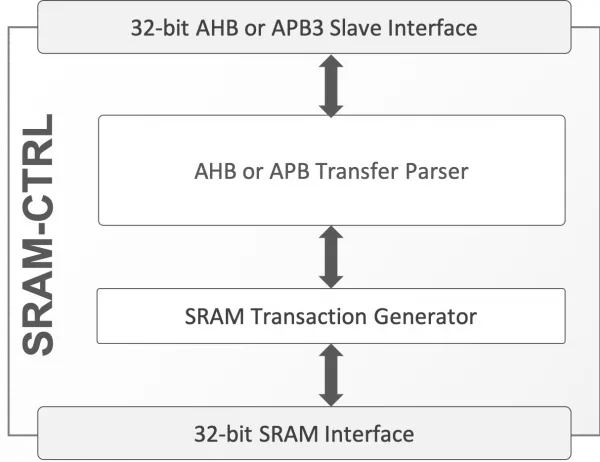

The SRAM-CTRL implements a Static Random Access Memory (SRAM) Controller translating AHB, or AXI4, or APB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM. The type of host interface is user-defined at synthesis time.

When the AHB interface is selected, the SRAM controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-to-back events: an AHB write directly followed by an AHB read. In this case, a single wait state is asserted.

When the AXI4 interface is selected, the SRAM controller provides zero-wait-state AXI4 access to the synchronous SRAM in all cases except in case when both AXI read and AXI write channel are active at the same time. In that case AXI write transfer is delayed.

When the APB interface is selected, the SRAM controller provides low latency APB access to the synchronous SRAM in all cases. APB write and read transfers are completed in two clock cycles.

The SRAM-CTRL core is rigorously verified, silicon-proven and available in RTL source or as a targeted FPGA netlist. It can be used in any SoC design, where a processor or some other module with an AHB, AXI or APB master interfaces needs to access one or more on-chip SRAMs.

The SRAM-CTRL as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

Key features

- Interfaces

- 32-bit host Interface compatible with either AMBA®, AHB, AXI4 or APB3 standards

- Standard 32-bit, single-port synchronous SRAM interface

- Easy to Use and Integrate

- Supports all types of AHB, AXI and APB transactions, including byte, half and word accesses

- Zero wait state / low latency operation

- No user programming required

- User-settable AHB/APB interface and endianness

- LINT-clean, scan-ready design

- Deliverables

- Synthesizable RTL or FPGA netlist

- Testbench & sample test cases

- Simulation & synthesis scripts

- Documentation

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DDR IP core

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Secure DDR DRAM Against Rowhammer, RAMBleed, and Cold-Boot Attacks

DDR IP Hardening - Overview & Advance Tips

Which DDR SDRAM Memory to Use and When

DDR5/4/3/2: How Memory Density and Speed Increased with each Generation of DDR

Frequently asked questions about DDR Controller IP cores

What is Static RAM Controller?

Static RAM Controller is a DDR IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this DDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.