SMBUS Assertion IP

SMBUS Assertion IP provides an efficient and smart way to verify the SMBUS designs quickly without a testbench.

Overview

SMBUS Assertion IP provides an efficient and smart way to verify the SMBUS designs quickly without a testbench. The SmartDV's SMBUS Assertion IP is fully compliant with standard SMBUS Specification.

SMBUS Assertion IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SMBUS Assertion IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Specification Compliance

- Supports SMBus specification version 3.0.

- Supports all the SMBus commands as per the specs.

- Supports programmable clock frequency of operation.

- Support ARP command generation and response.

- Support Timeout detection and generation.

- Bus-accurate timing.

- Packet Error Checking support.

- Wrong ARP Address

- Unsupported command codes

- Illegal command lengths

- Support for multiple instantiations to create complex verification environment.

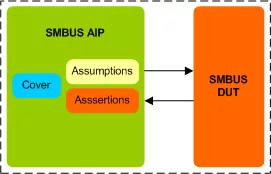

- Assertion IP features

- Assertion IP includes:

- System Verilog assertions

- System Verilog assumptions

- System Verilog cover properties

- Synthesizable Verilog Auxiliary code

- Support Master mode, Slave mode, Monitor mode and Constraint mode.

- Supports Simulation mode (stimulus from SmartDV SMBUS VIP) and Formal mode (stimulus from Formal tool).

- Rich set of parameters to configure SMBUS Assertion IP functionality.

Block Diagram

Benefits

- Runs in every major formal and simulation environment.

What’s Included?

- Detailed documentation of Assertion IP usage.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is SMBUS Assertion IP?

SMBUS Assertion IP is a I2C / I3C IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.