Simulation VIP for OctaRam

In production since 2018 for many production designs.The Cadence® Memory Model Verification IP (VIP) for OctaRam provides verific…

Overview

In production since 2018 for many production designs.

The Cadence® Memory Model Verification IP (VIP) for OctaRam provides verification of OctaRam and PSRAM controller using the OctaRam Double Data Rate RAM and PSRAM protocol. It provides a mature, highly capable compliance verification solution applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for OctaRam is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported specification: Features of the following vendors: Macronix, Micron, and APMemory. Micron uses the term PSRAM instead of OctaRam.

Key features

- Memory Size

- 16Mb to 512Mb

- SPI and Quad-SPI Mode

- Quad Entry: Switch mode of operation from SPI to QSPI

- Quad Exit: Switch mode of operation from QSPI to SPI for 16Mb and 64Mb Memory

- Reset

- Supports Hardware RESETn Pin and Software Global Reset command for PSRAM Device

- Power up Initialization

- Supports power up initialization with RESET pin as well as Global Reset command

- Read and Write

- Supports Identification Register Read

- Supports Memory Read and Write with Continuous and Wrapped Burst

- Supports Sync Read and Write with Wrapped and Hybrid Burst

- Supports Read and Write 64-byte Hybrid Wrapped Data for PSRAM

- Supports Read, Fast Read, Quad Read, Write, Quad Write for

- 16Mb and 64Mb devices in SPI mode without Wrapped Burst

- 16Mb Wrapped Read in SPI and QSPI mode with Wrapped Burst

- Supports x8 and x16 IO modes with Mode Register configuration

- Supports Linear burst with RBX feature

- Supports 16/32/64 byte wrap in x8 and 16/32/64/2K byte wrap in x16

- Supports 16/32/64 byte hybrid wrap

- Burst Length Toggle

- Switch the Wrapped Length to 32 byte from any value set in Mode Register 0 in SPI and QSPI mode for 16Mb Memory

- Preamble

- Supports Preamble Bit Patter Read command

- Power Down and Sleep

- Supports Deep Power Down operation

- Half Sleep Mode/Entry: Switch device In Ultra Low Power State

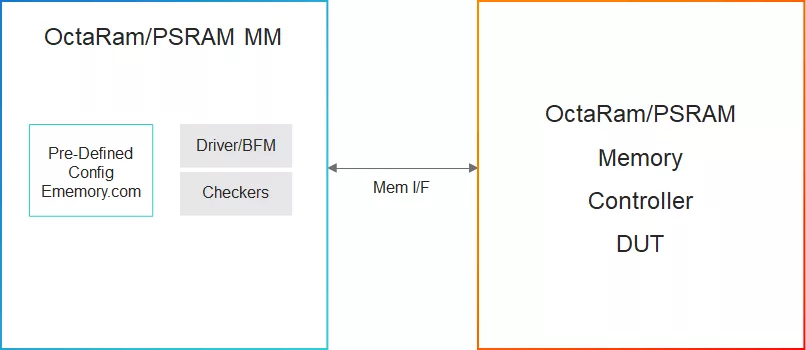

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about SRAM IP core

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Why SRAM PUF Technology Is the Bedrock of Dependable Security in Any Chip

AI-driven SRAM demand needs integrated repair and security

A comparison of SRAM vs quantum-derived semiconductor PUFs

Basics of SRAM PUF and how to deploy it for IoT security

Frequently asked questions about SRAM IP cores

What is Simulation VIP for OctaRam?

Simulation VIP for OctaRam is a SRAM IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SRAM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SRAM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.