Simulation VIP for eUSB

The Verification IP (VIP) for eUSB is a VIP solution for the Embedded USB2 (eUSB2) Physical Layer Supplement to the USB Revision …

Overview

The Verification IP (VIP) for eUSB is a complete VIP solution for the Embedded USB2 (eUSB2) Physical Layer Supplement to the USB Revision 2.0 Specification, Revision 1.1. It provides a mature and comprehensive verification IP (VIP) for the eUSB protocol. Incorporating the latest protocol updates, the eUSB2 VIP is not only just a complete bus functional model (BFM) for the DUT operating in eUSB Native Mode but it also provides integrated automatic protocol checks and coverage model.

This VIP for eUSB provides support for any eUSB device in native mode: Host(eDSPn) or Device(eUSPn), in Repeater Mode: Host(eDSPr) or Device(eUSPr), Host Repeater, Peripheral Repeater and Hybrid Repeater. . It supports all eUSB operational speeds: Low, Full, or High. It provides multiple signaling eUSB interfaces: single-ended signaling for low-/full-speed mode and low-voltage differential signaling for high-speed mode to test and monitor all possible configurations of USB devices. The eUSB VIP is designed in such a way that it is easy for you to integrate in testbenches for IP, System-on-chip (SOC) and system level. The eUSB VIP helps you to reduce time to test by accelerate verification closure and ensure end product quality.

The VIP for USB runs on all major simulators and supports all main verification languages such as Verilog, System Verilog and e alongside with industry-standard methodologies for Testbench writing such as Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported specifications: eUSB2 v1.1, USB2.

The following are the key features from the specifications that are implemented in the VIP:

|

Feature Name |

Description |

|---|---|

|

Supported DUT Types |

|

|

Transaction Types |

|

|

Backward Compatible |

|

|

Enumeration |

|

|

Operational Speed |

|

|

Reset Signaling |

|

|

Suspend/Resume |

|

|

Transaction and Packet Checks |

|

|

Protocol Features in Repeater mode |

|

|

Translator |

|

|

Register interface |

|

|

Predefined Error Injections |

|

Key features

- Support testbench languages for SystemVerilog, UVM, OVM, and e

- Runs on all major simulators

- Generation of constraint-random bus traffic

- Verify all device types: Host(eDSPn) or Device(eUSPn), Repeater Mode: Host(eDSPr) or Device(eUSPr), DUT as Hybrid Repeater.

- Dynamic activation and reconfigure the VIP attributes anytime during the simulation

- Built-in verification plan, protocol checks, and coverage model

- Callback access at multiple TX and RX queue points for Scoreboard and data manipulation

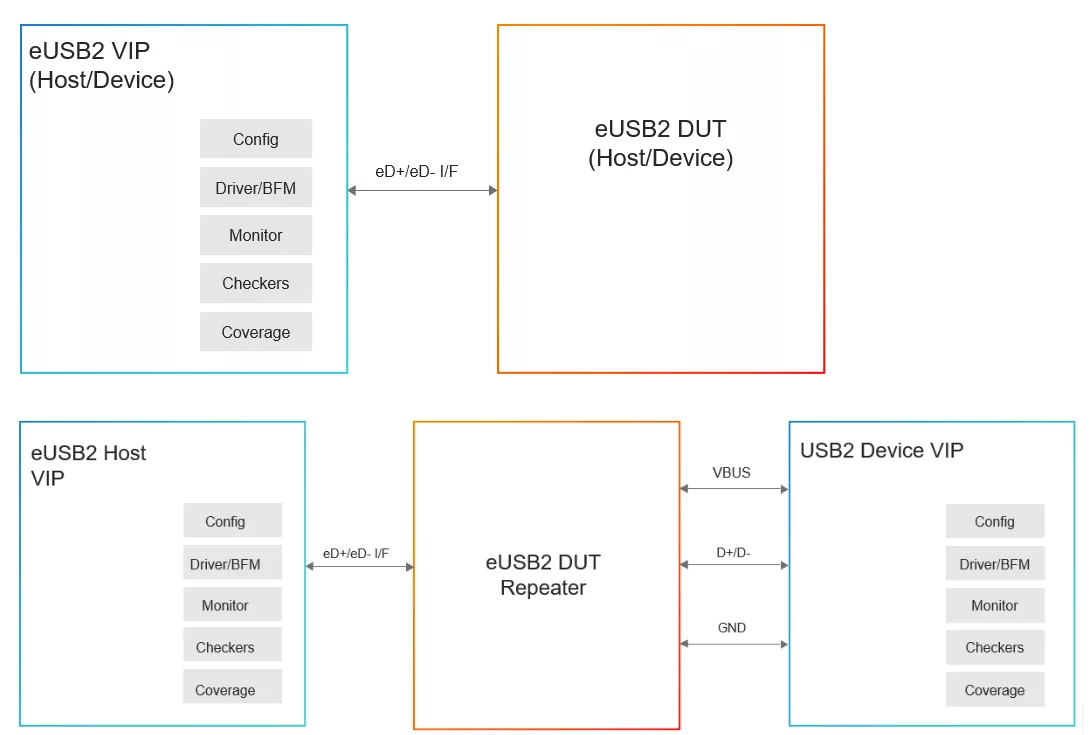

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is Simulation VIP for eUSB?

Simulation VIP for eUSB is a USB IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.