Verification IP for USB

Accelerated confidence in simulation-based verification of RTL designs with USB interfaces: UCM2, USB3.1, USB3.2, USB-C, Other US…

Overview

Accelerated confidence in simulation-based verification of RTL designs with USB interfaces: UCM2, USB3.1, USB3.2, USB-C, Other USB-C Protocols

Avery VIP for USB is a comprehensive solution for verification of USB-based designs ranging from the USB 2.0, 3.x, and 4.0 standards, including xHCI host controllers and USB mass storage class standards for UAS and BOT. USB VIP allows users to verify their designs by developing custom tests at several levels of abstraction.

Core through chip-level verification

The USB application designer can easily link the device under test (DUT) into the test environment, including DUT integration of the user-side logic to a USB protocol layer model. This enables full control over the DUT to initiate transac tions via HCDI operations. Device and PHY-only core verification is supported.

Compliance test suite

The test environment includes a suite of functional compliance tests for a simple USB device, UAS/BOT device, and xHCI host. Random and directed test cases are supported. Random testing supports generating random USB transfer types and PROTOCOL/LINK/PHY layer behaviors, including error injection.

Specifications

|

Protocol Family |

Standard Organization |

Sub Protocol |

Models |

|---|---|---|---|

|

USB4/3 |

USB-IF |

USB 4.0 |

|

|

USB-IF |

USB4 Logical CTS 1.1 |

||

|

USB-IF |

USB4 Protocol CTS 1.1 |

||

|

USB-IF |

USB 3.2 CTS |

||

|

xHCI |

USB-IF |

xHCI 1.2 |

|

|

PD |

USB-IF |

PD V3.0 R2.0 |

|

|

USB-IF |

PD V3.0 V1p14 r2 |

||

|

UAS/BOT |

USB-IF |

UAS 1.0 |

|

|

USB-IF |

UASP CTS 0.9 |

||

|

USB-IF |

BOT 1.0 |

||

|

T10 |

SBC4r12 |

||

|

T10 |

SPC5r12 |

||

|

T10 |

SAT3r04 |

||

|

T10 |

SAM6r02 |

||

|

USB2 |

USB-IF |

USB 2.0 |

|

|

USB-IF |

ULPI 1.2 |

||

|

USB-IF |

UTMI+ 1.0 |

Key features

- Complete solution for USB 2.0, OTG, Superspeed 4.0, Power Delivery (PD 3.0), and xHCI

- Runs over USB Type-C® interconnects

- Tunnels USB3, PCIe, and DP protocols

- Supports UAS/BOT core through SoC verification

- Host, device, and hub models

- PIPE/PHY models for USB3/USB2/PD with Type-C interface or SSIC/M-PHY

- Supports xHCI host controller IP development using xHCD host driver agent

- Compliance test suite for protocol, link, and physical layer verification of host, device, hub, and PHY

- Comprehensive assertions track USB compliance coverage

- Functional coverage tracks range of packet traffic, FSMs, and complex operational sequences

- Packet and symbol tracker monitor output to improve debug

Major features

- Host performs bus enumeration and allo cates USB pipes for communication between host and each endpoint

- Program TP sequences for bulk, isochronous, interrupt, bulk stream, and control transfer types

- Program USB device requests to access USB device descriptors

- Automatic frame scheduling and bus inter val and service interval support, including ITP generation

- Program host and device model timing parameters and response behaviors, such as link commands

- Fine-grained control over LTSSM transition sequences

- Fine-grained link layer controls

- Inject errors at all layers through callbacks

- Control device operation state transitions, including suspend/resume

- Full power management support (U0-U3), including automatic and software directed entry/exit

- Power on and inband reset

- xHC driver emulates hardware/software interface between system software and the host controller hardware

- xHC driver model implements all host side memory data structures and register-level host controller interfaces for USB 2.0/4.0, including complex randomized ring memory allocation

- xHC compliance test suite is also supported.

- The xHC driver VIP interfaces with xHC host controllers via PCIe and AMBA

- Mass storage class host implements the USB attached SCSI protocol (UASP) and bulk-only transport (BOT) protocols and supports the SCSI and task management commands found under SPC, SBC, RBC, and SAM

- Mass storage class test suite performs SCSI command compliance, performance, and power state verification, and provides cover age monitoring of the USB throughput and SCSI command completion status

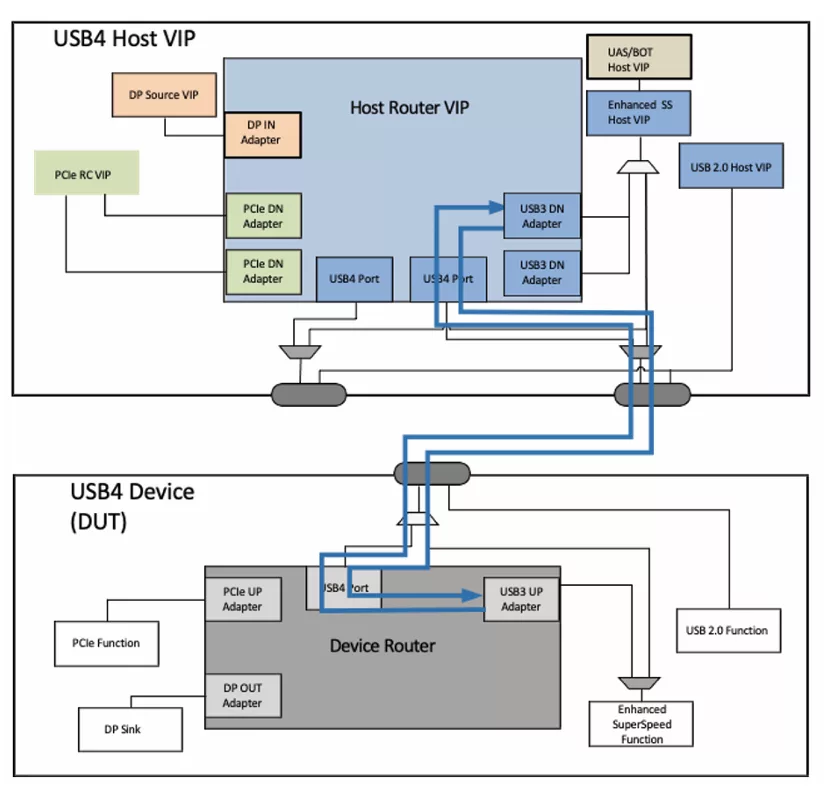

Block Diagram

Benefits

- Verifies USB-based designs

- Allows customized tests at several levels of abstraction

- Enables full control over the DUT to initiate transactions via HCDI operations

- Supports device and PHY-only core verification

- Supports random and directed test cases

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is Verification IP for USB?

Verification IP for USB is a USB IP core from Siemens Digital Industries Software listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.