USB OVA - USB 2.0 Function Controller OVA Checker IP

USB 2.0 Function Controller Checker OVA IP is fully documented, off the shelf component for the Developers of the USB 2.0 complia…

Overview

USB 2.0 Function Controller Checker OVA IP is fully documented, off the shelf component for the Developers of the USB 2.0 compliant Function Controller.

USB 2.0 OpenVera Assertions based Checker IP provides a concise, declarative mechanism to code the specification of sequences of events and activities of USB 2.0 Bus Protocol.

USB 2.0 OVA protocol rule Checker can work in a standalone mode i.e., can be plugged in any design verification environment, which uses the standard Protocol without disturbing the structure.

USB 2.0 OVA AIP Checker is developed using the abstraction in OVA syntax that is used in dynamic simulation of USB 2.0 based design.

OpenVera Assertions (OVA) provide fast and accurate way to simplify and speed up the device verification task. In a complex design process, verification may take up to 70% of the development time. OVA Checker AIP speeds up the verification process, thereby optimizing cost and time to market.

Product Specifications

- The AIP can be adapted to test a standard USB device in Synopsys Magellan Formal Verification environment.

- Supports PING Protocol.

- Supports SPLIT transactions.

- Supports SPLIT transactions.

Layered Approach

- A layered approach has been implemented in USB 2.0 OVA model to create a verification environment that allows sophisticated test scenarios.

- Layer 0: Logic and Events definitions - Booleans, events and variable definitions that are common to all USB 2.0 compliant devices are specified here.

- Layer 1: Individual templates for each of the Property corresponding to USB device are located in this layer.

- Layer 2: The common template from Layer 0 and individual templates from Layer 1 are instantiated here.

- Layer 3: This layer contains the `bind´ constructs meant for the OVA AIP Units and customized OVA AIP Header declarations.

Key features

- Fully compliant with the Universal Serial Bus Rev.2.0 specification. It accurately verifies the USB 2.0 protocol.

- The Checker AIP follows the OpenVera unified flow for formal tools.

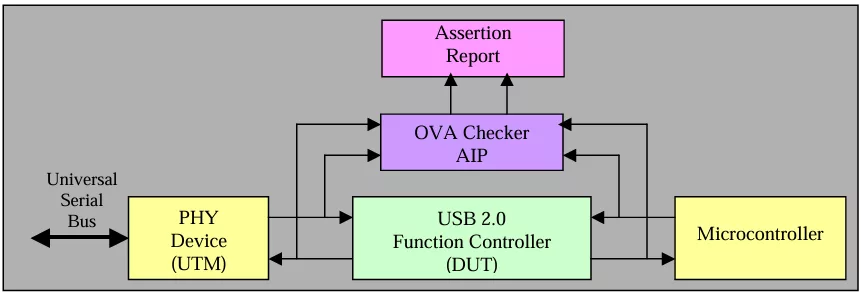

- The assertions are checked with the Universal Transceiver Macrocell Interface on the UTM side.

- The assertions are checked with the Generic Microcontroller Interface on Microcontroller side.

- Provides monitoring of signals and data in transmit and receive directions.

- Provides various error notifications based on the part of the protocol that gets violated such as ID and CRC errors.

- Supports Host, Hub and Device properties.

- Full programmability and versatility of the AIP allows connection to any standard USB device.

- Categorization of templates such as Host, Hub, Device, HostHubDevice, UTMI and UTMI16 allows selective turning ON and OFF of features while testing.

- The IP monitors the various transactions and their sequences.

- Provides transmit and receive sequencing error notification.

- Provides monitoring of signals and timings for reset, suspend and remote wake-up from the Host side.

- Provides monitoring of the Low speed, Full speed and High speed ports for all types of packets, fields, transactions and transfers. The checker IP incorporates layered approach.

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is USB OVA - USB 2.0 Function Controller OVA Checker IP?

USB OVA - USB 2.0 Function Controller OVA Checker IP is a USB IP core from Silicon Cores - a Div. of Silicon Interfaces listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.