MIPI GbD USB Verification IP

MIPI GbD USB Verification IP provides a smart way to verify the MIPI GbD USB component of a SOC or a ASIC.

Overview

MIPI GbD USB Verification IP provides a smart way to verify the MIPI GbD USB component of a SOC or a ASIC. It provides backward compatibility support for earlier versions 1.0 and 1.1 of USB specifications. The SmartDV's MIPI GbD USB 1.0/1.1 Verification IP is fully compliant with standard USB Specification 3.0/3.1/3.2 and MIPI Giga bit data with USB version 1.0/1.1. The MIPI GbD USB 1.0/1.1/ VIP can be readily customized and optimized for a wide range of specific system applications.

MIPI GbD USB Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

MIPI GbD USB Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compliant with MIPI Giga bit debug specification version 1.0/1.1

- Supports the network adaptor for USB

- Supports the trace applications

- Supports the Sneak peak applications

- Supports the memory map in application layer

- Supports both Debug Test System(DTS) and Target System(TS)

- Includes Trace Wrapper Protocol(TWP)

- Includes Sneak Peak Protocol(SPP)

- Supports Giga bit trace data

- Includes USB logical device for connecting Target system(TS) Network Adaptor to a USB Device Controller

- Complete solution for thorough chip-level verification

- Supports all types of error injection and detection

- USB 3.0/3.1/3.2 Common support

- Configurable PHY Interface width 8, 16 or 32 bits

- PHY interface supports data scrambling to reduce EMI emissions

- Comprehensive compliance testsuite for Protocol, Link, and Physical layer verification

- Supports Low frequency periodic signaling (LFPS) for initialization and power management(U1, U2 & U3)

- Supports Interrupt/Bulk/Isochronous/Control Transfers

- Control transfers supported by Endpoint 0

- Separate Endpoint Buffers for IN bound and OUT bound packets

- Supports for USB 3.0/3.1/3.2 low power states

- Bulk Stream support

- Supports Lane polarity inversion

- Supports eXtensible Host Controller Interface

- Comprehensive model support a Host, Device, Hub, PHY

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

- Supports constrained randomization of protocol attributes

- USB 3.0 support

- Compliant with USB 3.0 specification.

- Compliant with USB 3.0 Super speed Inter chip supplement 1.0.

- USB 3.0 host and device with SERIAL/PIPE/SSIC interfaces

- Supports dual-simplex, four-wire differential signaling and 8b/10b parallel interface

- Operates at Super speed (5 Gbit/s), High(480 Mbit/s) or Full speed(12 Mbit/s) modes

- Supports SS-OTG,SSPC-OTG Devices,SS-PO Devices and SS-EH Devices

- Supports ADP,HNP,SRP and RSP

- USB 3.0 host and device with SERIAL/PIPE/SSIC interfaces

- Supports Inter-Chip Supplement to the USB Revision 3.0 Specification (Super Speed Inter-Chip) using MIPI MPHY

- Supports MPHY Type-I operations

- Supports MPHY all PWM 1 gear of operation

- Supports MPHY all HS 1,2,3 gear of operation

- Supports 1,2,4 lanes

- Supports all types of error injection in MPHY

- Supports All RRAP Packet types

- Supports LS and HS burst

- Supports all LS and HS gears

- Supports all protocol error detection

- Supports all MPHY protocol error injection

- Supports RMMI and MPHY serial interface

- Supports UTMI and PIPE interfaces.

- USB 2.0 device and host with UTMI/ULPI interfaces.

- Supports all types of error injection and detection.

- Supports error injection in all the layers of USB 3.0.

- Supports constrained randomization of protocol attributes.

- On-the-fly protocol and data checking.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Built in coverage analysis.

- Callbacks in host and device for various events.

- Status counters for various events.

- USB 3.0/3.1 Verification IP comes with complete testsuite to test every feature of USB 3.0/3.1 specification.

- xHCI support

- USB 3.0 OTG

- Supported devices.

- 1.SS-OTG

- 2.SSPC-OTG Devices

- 3.SS-PO Devices

- 4.SS-EH Devices

- Support for USB 2.0.

- 1.SS-OTG or SSPC-OTG devices operate as USB 2.0 OTG devices.

- 2.SS-EH operate as USB 2.0 EH.

- 3.SS-PO operate as USB 2.0 PO devices.

- Supported protocols.

- 1.SRP

- 2.HNP

- 3.ADP

- 4.RSP for USB 3.0

- Supported speeds.

- 1.SS,HS and FS

- Supported feature selector

- 1.b_hnp_enable

- 2.a_hnp_support

- 3.a_alt_hnp_support

- 4.NTF_HOST_REL

- 5.B3_RSP_ENABLE

- Support the all timeout condition

- 1.a_wait_vfall_timout

- 2.a_wait_vrise_timout

- 3.a3_polling_tmout

- 4.a3_recovery_tmout

- 5.a3_rx_detect_active_tmout

- 6.rsp_cnf_err_tmout

- 7.rsp_ack_err_tmout

- 8.rsp_wrst_err_timout

- 9.b3_polling_tmout

- 10.b3_recovery_tmout

- 11.b3_rx_detect_active_tmout

- Combination of SSPC-OTG device communication

- 1.SSPC-OTG device to SSPC-OTG device

- 2.SSPC-OTG device to SS-OTG device

- 3.SS-OTG device to SSPC-OTG device

- 4.SSPC-OTG device to USB 2.0 OTG

- 5.USB 2.0 OTG device to SSPC-OTG device

- USB 3.1 support

- Compliant with USB 3.1 specification version 1.0

- Supports dual-simplex, four-wire differential signaling and 128b/132b parallel interface

- Operates at SuperSpeedPlus (10 Gbit/s), Super speed (5 Gbit/s), High speed(480 Mbit/s) or Full speed(12 Mbit/s) modes

- Backward compatible with USB 3.0

- USB 3.1 host and device with SERIAL/PIPE interfaces

- Supports specific LFPS patterns(SCD1/SCD2) for Super speed plus ports

- Supports SuperSpeedPlus LFPS Based PWM Message (LBPM)

- Supports SuperSpeedPlus Precision Time Measurement

- Supports SuperSpeedPlus Transaction Reordering for periodic and asynchronous packets

- USB 3.2 support

- Supports dual-lane for Gen1 and Gen2

- Backward compatible with USB 3.1 and USB 3.0

- USB 3.2 host and device with dual-lane SERIAL/PIPE interface

- Supports Deskew

- Supports Data striping in dual lanes

- Supports dual-simplex, four wire differential signaling and 128b/132b parallel interface

- Supports Configuration summary descriptor

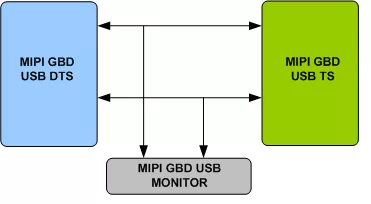

Block Diagram

Benefits

- Rich set of configuration parameters to control the functionality

- Faster testbench development and more complete verification of MIPI GBD for USB 3.0/3.1/3.2 designs.

- Easy to use command interface simplifies testbench control and configuration of host and device.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the MIPI GBD USB 3.0/3.1/3.2 testcases.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is MIPI GbD USB Verification IP?

MIPI GbD USB Verification IP is a USB IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.