eUSB Verification IP

eUSB Verification IP provides an smart way to verify the eUSB component of a SOC or a ASIC.

Overview

eUSB Verification IP provides an smart way to verify the eUSB component of a SOC or a ASIC. It provides backward compatibility support for earliers versions 1.0 and 2.0 of USB specifications. The SmartDV's eUSB Verification IP is fully compliant with standard Embedded USB2 (eUSB2) Physical Layer Supplement to the USB Revision 2.0 Specification Rev.1.1 and USB 1.1/USB 2.0 Specification.

eUSB VIP data transfer can be done at different speeds. Which intuitively involves high speed(480 Mbit/s), full speed(12 Mbit/s) or low speed(1.5Mbit/s). The eUSB VIP includes an extensive test suite covering most of the possible scenarios. It performs all possible protocol tests in a directed or a highly randomized fashion which adds the possibility to create the widest range of scenarios to verify the DUT effectively. This way it detects the violation of protocol completely.

eUSB Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

eUSB Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- eUSB

- Compatible with Embedded USB2 (eUSB2) Physical Layer Supplement to the USB Revision 2.0 Specification Rev.1.1.

- Fully compliant to the USB2.0 layer architecture with the following features:

- Supports high-speed, full-speed, and low-speed operation.

- High-speed: Low voltage differential signaling.

- Low-speed/Full-speed: Single-ended digital low-voltage signaling.

- Supports selected single speed configuration in native mode.

- Supports USB2.0 operation based on repeater architecture.

- Supports link power management LPM-L1 (L1) and Suspend (L2).

- Supports register access protocol (RAP) for eUSB device or repeater configurations.

- Fully compliant to USB2.0 base spec at the protocol layer.

- Supports Host and Peripheral model.

- USB 2.0

- Compatible with USB 1.1 and USB 2.0 specification

- Supports Standard USB 2.0 interface, UTMI, UTMI+, ULPI and HSIC interfaces.

- Standard DP/DM bus interface is supported.

- Operates at high, full and low speed.

- Support HOST and Device model.

- Supports up to 127 devices.

- Supports completely configurable bus enumeration.

- Supports all descriptor types and device requests.

- Supports Link Power Management (LPM).

- Supports constrained randomization of protocol attributes.

- All USB2.0 transfer types (Control, Isochronous, Interrupt, Bulk) are supported.

- Supports both transaction level (Setup, In, Out, Ping) and packet level (Token, Data, Handshake, SOF) transmission/reception.

- Constrained driven randomization of packets achieved by randomization of various fields of the packet.

- Auto detection of device connection and disconnection.

- Supports SRP and HNP compliance checking.

- Provides SOF generation support.

- Programmable inter packet and end-to-end delays.

- Proficiency to generate random packets/transactions and respond to packets/transactions in directed or randomized fashion.

- Supports all types of error injection and detection. Errors include:

- Corrupt Sync byte

- Corrupt PID Byte

- Corrupt CRC-5 Byte

- Corrupt CRC-16 Byte

- Corrupt Endpoint Address Byte

- Corrupt Setup Payload Size

- Corrupt Setup Stage Data Payload

- Corrupt EOP byte

- Bit stuffing error.

- Programmable timers for suspend, resume and reset signaling.

- USB 2.0 OTG

- Combination of OTG device communication

- OTG device to Embedded Host

- Targeted Host to peripheral only B-device

- OTG device to OTG device

- Supported devices

- Dual A device

- Dual B device

- Embedded host

- SRP only B device

- Supported protocols

- SRP

- HNP

- HNP polling

- Suspend/Resume/Remote wakeup

- ADP

- Supported speeds

- HS and FS

- Supported feature selector

- b_hnp_enable

- a_hnp_support

- a_alt_hnp_support

- Support the all timeout condition

- a_wait_vrise_tmout

- a_wait_vfall_tmout

- a_wait_bcon_tmout

- a_aidl_bdis_tmout

- a_bidl_adis_tmout

- Support for bus drop and over current condition

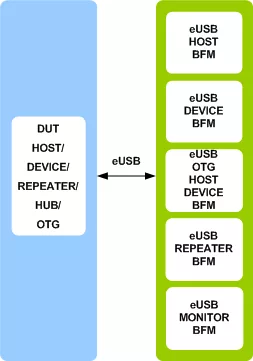

Block Diagram

Benefits

- Faster testbench development and more complete verification of eUSB designs.

- Easy to use command interface simplifies testbench control and configuration of Device and Host.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the eUSB testcases.

- Examples showing how to connect various components and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is eUSB Verification IP?

eUSB Verification IP is a USB IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.