Simulation VIP for DSC

The Cadence® Verification IP (VIP) for Display Stream Compression (DSC) provides an ability to perform comprehensive verification…

Overview

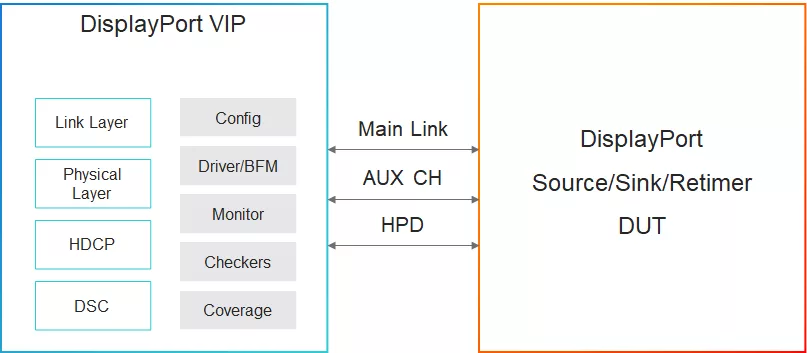

The Cadence® Verification IP (VIP) for Display Stream Compression (DSC) provides an ability to perform comprehensive verification of DSC-related features of display protocols. This product complements the Cadence VIP for MIPI DSI and VIP for DisplayPort and must be used with one of them. The Cadence VIP for DSC is compatible with all main verification languages (such as Verilog, SystemVerilog, e, VHDL, C, SystemC®, and Vera) and industry-standard methodologies (such as UVM, OVM, and VMM), and runs on all leading simulators. DSI VIP complements the Cadence VIP for MIPI DSI and VIP for DisplayPort.

Supported specification: VESA DSC 1.1, 1.2, and 1.2a.

Key features

- DisplayPort

- DSC Version

- DSC 1.2a (VBR is not supported by the DP specification)

- Configuration

- Discovery, Enabling, Disabling

- Framing and Compressed Stream Mapping

- 1, 2, 4, 8, 12, 16, 20, 24 slices per line

- Picture Parameter Set (PPS) Packet

- PPS packet header and payload

- DSC DPCD Fields

- All DSC related registers are supported

- PSR in DSC

- PSR SDP and PSR2 Selective Update in DSC Configuration

- MIPI DSI-2

- DSC Version

- DSC 1.1, DSC 1.2

- Decoding Process

- Video encoded frames are decoded by VIP monitor

- Encoding Process

- Active Processor VIP generates encoded video frames using DSC algorithm

- Format of DSI Packets

- Verifies format correctness of DSI packets related to DSC

- Content of DSI Packets

- Verifies content correctness of DSI packets related to DSC

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about VESA DSC IP core

MIPI: Powering the Future of Connected Devices

VESA Video Compression on MIPI DSI-2 Enables Next-Generation Display Applications

Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

Revolutionizing Display Technology with VESA Display Stream Compression (DSC) Decoder IP

VESA Display Stream Compression (DSC) Encoder IP Core

Frequently asked questions about VESA DSC IP cores

What is Simulation VIP for DSC?

Simulation VIP for DSC is a VESA DSC IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this VESA DSC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this VESA DSC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.