Serial Flash Synthesizable Transactor

Serial Flash Synthesizable Transactor provides an smart way to verify the Serial Flash component of a SOC or a ASIC in Emulator o…

Overview

Serial Flash Synthesizable Transactor provides an smart way to verify the Serial Flash component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's Serial Flash Synthesizable Transactor is fully compliant with standard Serial Flash Specification and provides the following features.

Key features

- Follows Serial Flash specification as defined in WINBOND, MICRONIC, MACRONIX, MICRON, SPANSION, Silicon Storage technology (SST) and many more

- Supports software and hardware Reset

- Supports quad peripheral interface (QPI) reduces instruction overhead

- Supports allows true XIP (execute in place) operation

- Supports program 1 to 256 byte per programmable page

- Supports erase/program suspend & resume

- Supports software and hardware write-protect

- Supports discoverable parameters (SFDP) register

- Supports volatile & non-volatile Status Register Bits

- Supports advanced security features

- Supports 3-wire,4-wire interface

- Supports baud rate selection

- Supports burst modes

- Supports fast read and byte program

- Supports block/sector protection

- Supports flexible erase operation like,

- 4KByte sector erase

- 32KByte block erase

- 64KByte block erase

- Supports internal clock division check

- Supports security ID

- Supports on the fly generation of data

- Supports backdoor initialization of data

- Notifies the test bench of significant events such as transactions, warnings, and protocol violations. This can be written to separate log files

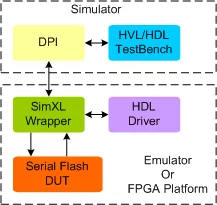

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the Serial Flash testcases

- Examples showing how to connect and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Test / Debug IP core

Metric Driven Validation, Verification and Test of Embedded Software

Tools for Test and Debug : Embedded designers face a myriad of multiprocessor challenges

eUSB2V2: Trends and Innovations Shaping the Future of Embedded Connectivity

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Arasan’s xSPI/eMMC5.1 PHY: Unified Dual-Mode Physical Layer IP

Frequently asked questions about SerDes Test / Debug IP cores

What is Serial Flash Synthesizable Transactor?

Serial Flash Synthesizable Transactor is a Test / Debug IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Test / Debug?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Test / Debug IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.