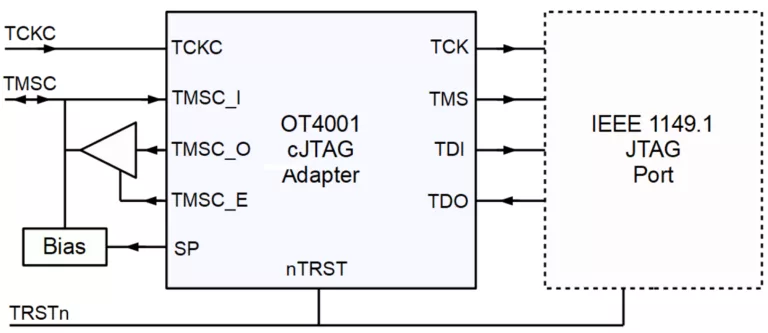

JTAG 2-Wire to 4-Wire Adapter

The OT4001_cjtag is an adapter which permits legacy IEEE 1149.1 ports to communicate as an IEEE 1149.7 2-wire OScan1 cJTAG port.

Overview

The OT4001_cjtag is an adapter which permits legacy IEEE 1149.1 ports to communicate as an IEEE 1149.7 2-wire OScan1 cJTAG port. A simple update to a 1149.1 port to support 1149.7 2-wire signaling. This can be used for reduction in pin count for chips with JTAG interfaces. The IP is in the form of synthesizable verilog. May be implemented in ASIC or FPGA.

Key features

- IEEE 1149.1 and IEEE 1147.7 compatible.

- Small logic overhead.

- Clock frequencies to 25MHz.

- Activated with a 12b Online Activation Code.

- Available setup support code for Digilent SDK and OpenOCD.

- Available CPLD for test system debug prior to silicon.

- Delivered as obfuscated verilog.

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- Founded 1995

- Privately owned consulting company

- Diversified customer base

- Self funded

- Early delivery of front-end models.

- On-site support available, including transfer of source to your design environment.

- Available on-site design review.

- On-site training for source licensing.

- Option to take ip though your own quality and review processes.

- Characterization support.

- Fast and flexible legal. We typically accept your standard bi-directional NDA.

- Simple plain-language contracts.

Learn more about Test / Debug IP core

Metric Driven Validation, Verification and Test of Embedded Software

Tools for Test and Debug : Embedded designers face a myriad of multiprocessor challenges

Securing Scale-Up AI: Cadence’s Complete UALink Solution

eUSB2V2: Trends and Innovations Shaping the Future of Embedded Connectivity

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Frequently asked questions about SerDes Test / Debug IP cores

What is JTAG 2-Wire to 4-Wire Adapter?

JTAG 2-Wire to 4-Wire Adapter is a Test / Debug IP core from Obsidian Technology listed on Semi IP Hub.

How should engineers evaluate this Test / Debug?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Test / Debug IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.