32Gbps, 7/15/31 order, Pseudo Random Bit Sequence Generator/Checker

This unit generates and checks Pseudo Random Bit Sequence (PRBS) of 7, 15 or 31 order, up to 32Gbps.

Overview

This unit generates and checks Pseudo Random Bit Sequence (PRBS) of 7, 15 or 31 order, up to 32Gbps. Error count is accurate: no double counts or omissions regardless of error sequence or frequency of occurrence. Can be used as Generator, Checker or both. No inductors are used minimizing area and EM interference. Simple control interface, with low frequency asynchronous signals only.

Key features

- PRBS order: 7, 15 or 31 based on formulas: X1=X6^X7; X1=X14^X15; X1=X28^X31

- Full bit rate at input and output up to 32Gbps

- Generator, Checker and Counter functions

- Accurate error count: no omissions or double counts

- Full rate CMOS differential input data, centered with half-rate CMOS differential clock

- Full rate CMOS differential output data, aligned with half-rate CMOS differential clock

- Asynchronous low frequency CMOS control interface

- Supply voltage: 0.9V

- Typical power consumption: 80mA at 32Gbps in simultaneous Generator and Checker mode; scales with bit rate

- Power down mode

- Error counter ready indicator signal

- Operational temperature range: -40C to +110C

- Footprint: 65 x 140 um

- Process: TSMC 28nm HPC/HPC+, portable to more advanced processes

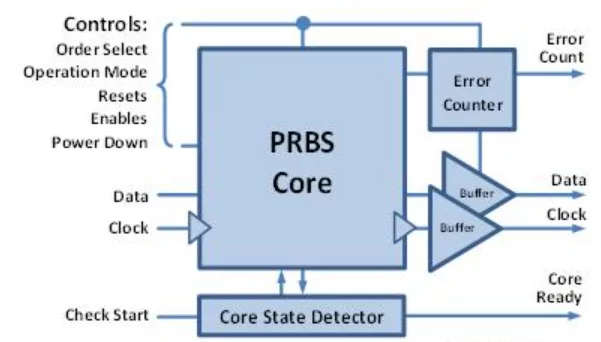

Block Diagram

Benefits

- Direct high-speed PRBS generation and checking

- Embedded accurate Error Counter

- Compact footprint, no inductors, minimal EM interference

- Simple, asynchronous interface, easy transition between clock domains

- Easily portable to more advanced technology

- Facilites faster implementation of advanced flexible built-in self-test (BIST)

- Reduces the need of expensive testing equipment

- Eliminates on-wafer high-speed test

Applications

- Unit is intended for testing of communication channels and clock/data recovery systems. Helps to verify functionality and evaluate channel and system quality and efficiency by measuring bit error rates. Unit fits well with Design for Test (DFT) approach and makes an irreplaceable element of advanced Built-in Self Test (BIST) systems.

What’s Included?

- Technical Brief - TB

- Data Sheet - DS

- Application Note - AN

- Models: Verilog-AMS, Spectre (CC extracted), Spectre (back-annotated)

- Demo Testbenches - DTB (OA schematics)

- GDSII Black Box

- GDSII

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | 28nm 280 nm | — |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Test / Debug IP core

Metric Driven Validation, Verification and Test of Embedded Software

Tools for Test and Debug : Embedded designers face a myriad of multiprocessor challenges

Securing Scale-Up AI: Cadence’s Complete UALink Solution

eUSB2V2: Trends and Innovations Shaping the Future of Embedded Connectivity

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Frequently asked questions about SerDes Test / Debug IP cores

What is 32Gbps, 7/15/31 order, Pseudo Random Bit Sequence Generator/Checker?

32Gbps, 7/15/31 order, Pseudo Random Bit Sequence Generator/Checker is a Test / Debug IP core from Kamaten Technology Incorporated listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Test / Debug?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Test / Debug IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.