A-PHY v1.1 Verification IP

The MIPI A-PHY Verification IP provides an effective & efficient way to verify the components interfacing with MIPI A-PHY interfa…

Overview

The MIPI A-PHY Verification IP provides an effective & efficient way to verify the components interfacing with MIPI A-PHY interface of an IP or SoC. The MIPI A-PHY VIP is fully compliant with MIPI Alliance specification for A-PHY Version 1.1.1 with APPI interface. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time

Key features

- Compliant to MIPI A-PHY Specification Version 1.1.1 with APPI interface.

- Support all C-Port, D-Port and Q-Port.

- Support for both Profile 1 and Profile 2.

- Supports all possible configuration for Data Lane Module at PHY layer.

- Supports configurable number of Data Lane for PAM.

- Supports all modes of operation, Highly Asymmetric mode, Asymmetric mode, Symmetric mode, Q-Fallback Highly Asymmetric mode.

- Support for ACMD and ACMP.

- Support PAM-X and NRZ-8b/10b modulation schemes.

- Support CSI2, DSI2, eDP-DP, ETH, GPIO, SPI and I2C native protocol.

- Support for Local Functions, Multi-Port Functions and Network Functions.

- Support Multiple speed gears ranging from 2 Gbps up to 16 Gbps.

- Supports Downlink, Reverse Downlink, Uplink communication.

- Supports Local Retransmission mechanism.

- Can be configured for normal and error scenarios.

- A wide variety of error injections.

- Functional Coverage of all configurations.

- Callback for user control.

- Support dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using assertions.

- Built in Coverage analysis.

- Graphical analyser to show transactions for easy debugging

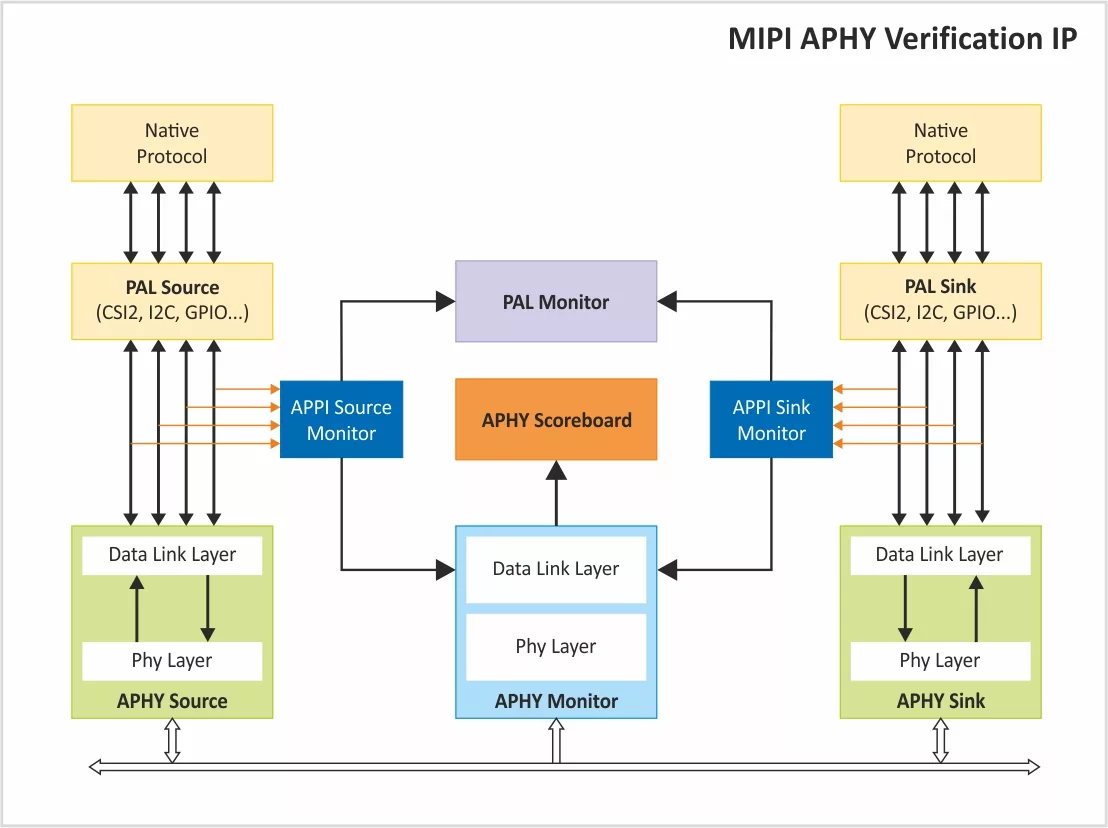

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Conformance and Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

What’s Included?

- MIPI A-PHY TX / RX BFM/Agent

- MIPI A-PHY Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random and Dynamic Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Conformance Tests

- Integration Guide, User Manual, and Release Notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about Test / Debug IP core

Metric Driven Validation, Verification and Test of Embedded Software

Tools for Test and Debug : Embedded designers face a myriad of multiprocessor challenges

eUSB2V2: Trends and Innovations Shaping the Future of Embedded Connectivity

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Arasan’s xSPI/eMMC5.1 PHY: Unified Dual-Mode Physical Layer IP

Frequently asked questions about SerDes Test / Debug IP cores

What is A-PHY v1.1 Verification IP?

A-PHY v1.1 Verification IP is a Test / Debug IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this Test / Debug?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Test / Debug IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.