SD/SDIO 2.0 MMC Host Controller

The EP550 is a host controller for SD memory card, SDIO and MMC interface.

Overview

The EP550 is a host controller for SD memory card, SDIO and MMC interface. The core connects the host CPU of the system to the SD card socket. External SD cards can be accessed by the host CPU through the EP550 controller core IP.

SD memory and SDIO are low cost, high speed interfaces designed for removable mass storage and IO devices. It is a very flexible architecture supporting variable clock rate from 0 to 25Mhz and data width of 1 to 4 bits. A data rate of up to 12.5Mbyte/sec (100Mbs) can be realized with SD interface. Features such as plug and play, auto-detection, error correction, write protection are standard with SD card interface.

The EP550 SD card host controller core is designed according to the SD Association’s SD host controller specification. The core presents a very simple view of the SD card to the system software. All access to the SD card are made through the standard control register set. DMA, burst access, CRC error detection, interrupt, timing, etc. are supported by the controller core. Because of the standard register set, the EP550 can be used to replace other existing SD controllers with no change to system software.

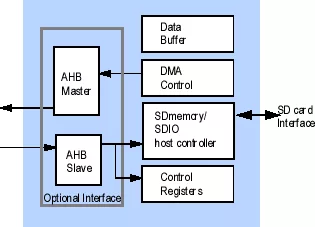

There are several options for user hardware interface to the controller core. The controller supports generic user interface optimized for on-chip logic interface as well as embedded CPU interface such as AMBA AHB bus. To access the SD card, the host CPU simply issue read/write access to the control registers in the core. The controllers core handles all the SD card protocol automatically including data shifting, timing and CRC generation. The core has a built-in DMA controller so that data can be automatically transferred between the system and the SD card without CPU intervention.

With the EP550, SD card interface can be realized with very little development cost. Designer can add SD memory and SDIO interface to the system by simply adding the EP550 module without changing the rest of the system architecture.

Key features

- Host controller for SDIO, SD memory card, and MMC interface.

- Allows host CPU to access SD and MMC devices.

- Simple user interface optimized for on-chip bus connection.

- User interface supports 32-bit and 64-bit data.

- Option to integrate with other CPU bus slaves to support direct access by various CPU’s including PowerPC, MPC860, ARM, SH2/3/4, MIPS, and ARC microprocessors.

- Supports SDIO DMA operation for high speed data transfer.

- Supports SD host controller standard register set.

- Fully programmable access timing.

- Supports multi-function SD cards, command suspend, resume, and block transfers.

- Option to operate the user interface and card interface at different clock domains.

- Direct mapping of host address space to card address space.

- Designed for ASIC and FPGA implementations.

- Fully static design with edge triggered flip-flops.

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- Shorten Time-to-market

- Eliminate Design Risks

- Reduce Development Costs

Learn more about SD / eMMC Controller IP core

Virtual Prototyping Platform with Flash Memory

Allowing server-class storage in embedded applications

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Frequently asked questions about SD / eMMC Controller IP cores

What is SD/SDIO 2.0 MMC Host Controller?

SD/SDIO 2.0 MMC Host Controller is a SD / eMMC Controller IP core from Eureka Technology, Inc. listed on Semi IP Hub.

How should engineers evaluate this SD / eMMC Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SD / eMMC Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.