PCIe 7.0 Controller with AXI

The PCI Express® (PCIe®) 7.0 Controller with AXI is a configurable and scalable design for ASIC implementations.

Overview

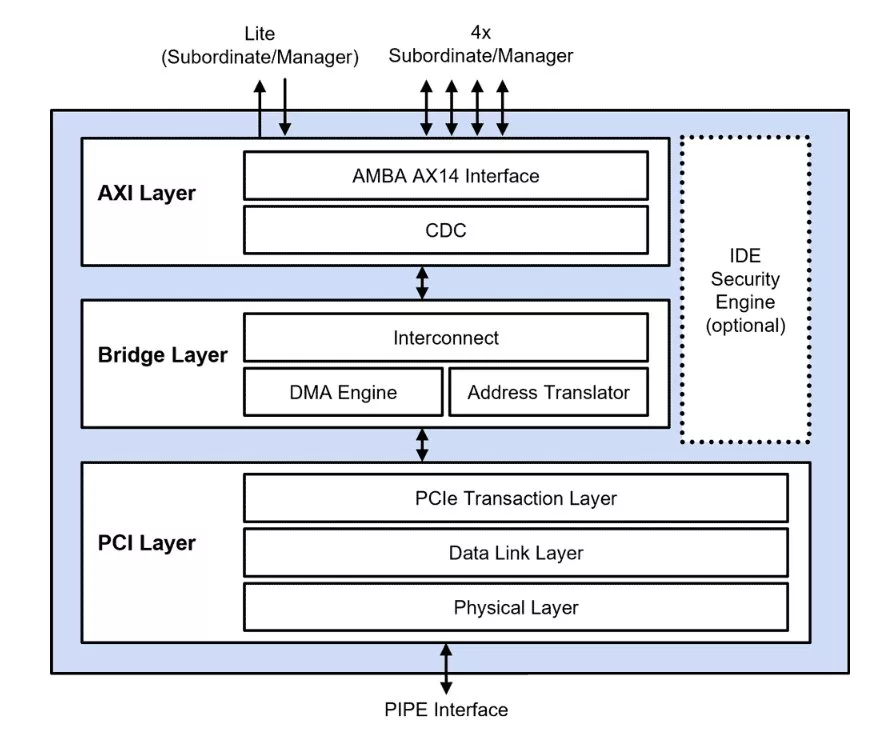

The PCI Express® (PCIe®) 7.0 Controller with AXI is a configurable and scalable design for ASIC implementations. Optimized for high-bandwidth efficiency at data rates up to 128 GT/s, the controller delivers maximum performance for Data Center, Edge, AI/ML and HPC applications. It is backward compatible to the PCIe 6.0 and 5.0, as well as version 6.2.1 PHY Interface for PCI Express (PIPE) specification.

Key features

- Optimized for high-bandwidth efficiency at data rates up to 128 GT/s

- Separate native TX/RX data path separating posted/Non posted/completion traffic

- Handles up to 4 TLPs per cycle

- Advanced PIPE modes and port bifurcation

- Supports multiple virtual channels

- Supports Endpoint, Root-Port, Dual-mode, Switch port configurations

- Advanced RAS features

- Optional IDE security with AES-GCM encryption, decryption and authentication

- Supports AMBA AXI interconnect

Block Diagram

What’s Included?

- IP Files

- Verilog RTL source code

- Libraries for functional simulation

- Configuration assistant GUI (Wizard)

- Full Documentation

- Reference Designs

- Synthesizable Verilog RTL source code

- Simulation environment and test scripts

- Synthesis project and DC constraint files (ASIC)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PCI Express IP core

Realizing the Performance Potential of a PCI-Express IP

Navigating the Complexity of Address Translation Verification in PCI Express 6.0

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Frequently asked questions about PCIe IP cores

What is PCIe 7.0 Controller with AXI?

PCIe 7.0 Controller with AXI is a PCI Express IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.