OpenGL ES 2.0 3D graphics IP core for FPGAs and ASICs

D/AVE NX is the latest and most addition to the D/AVE family of rendering cores.

Overview

D/AVE NX is the latest and most powerful addition to the D/AVE family of rendering cores. It is the first IP to bring 3D graphics OpenGL ES 2.0 rendering (with some ES 3.0 / 3.1 extensions) to the FPGA and SoC world and – with offline-shader compilers – even into MCUs or low-end MPUs with small amounts of memory and bare-metal or RTOS operation systems.

Targeted for graphics applications on displays up to 4K x 4K resolution in the Industrial, Medical, Military, Avionics, Automotive and Consumer markets, D/AVE NX is designed to meet the sweet spot of performance and footprint bringing full 3D graphics even down to MCU class devices and into safety critical applications.

By enabling the use of programmable shaders even on small devices, high quality 2D and full 3D applications can be realized using the D/AVE NX core. Support for industry standard APIs like OpenGL ES 2.0 allows for rapid development of high-end user interfaces by leveraging common GUI frameworks like LVGL, Qt, SCADE or Guiliani and makes new, future-proof implementations possible.

D/AVE NX can scale easily to fit exactly into the resource / performance sweet spot for a particular application. Entire device families can be equipped with differently scaled variants of the core, making all of them fully software-compatible. A single unified software stack and the guarantee to produce exactly the same visual result (at different speeds) allows saving significant development resources.

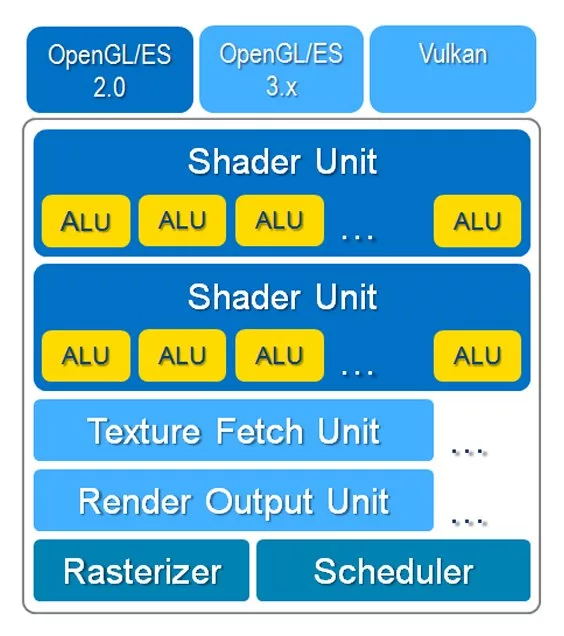

D/AVE NX is highly efficient as the internal multi-level scheduler can maximize the utilization of every hardware element even better than the fixed function pipeline of the successful D/AVE-2D and -HD cores could. Scheduling also does not have to be precomputed in the compiler, simplifying the compiler and driver architecture considerably.

D/AVE NX Graphics Turnkey System Solution for Altera SoCs

D/AVE NX is provided within evaluation kits for Altera Arria10 and Agilex 5 SoCs including a complete solution based on Yocto Linux and Qt as well as OpenGL ES 2.0 example applications. The evaluation kits include the D/AVE NX QSys component, drivers and documentation, i.e. everything that is needed for integration, evaluation and prototyping purposes.

Key features

System Features

- Scalability throughout the entire design

- 1 - 4 shader units

- 4 - 32 ALUs per shader unit (2 operations per ALU per cycle)

- Optional Special-Function & I/O Units

- Configurable cache sizes and optional 2nd level cache

- Up to 4k resolution

- Exact same driver can be used on all versions – enables the same output at different speeds

- Unified Shader Architecture

- Fully IEEE compatible floating point ALUs

- True integer arithmetic (8bit, 16bit, 32bit)

- Massively parallel execution with fine grained Multithreading

- Immediate mode rendering (no need to buffer entire scene description)

- Application optimization and debugging support

- Pipelined architecture for high clock frequencies

- System security features

Rendering

- OpenGL ES 2.0 API

- with some OpenGL ES 3.0 / 3.1 extensions

- Partial screen updates

- OpenGL extensions for flash-based textures

- Optional offline shader compilation

- High render quality

- Highly accurate sub pixel positioning, interpolation, and filtering

- Multiple anti-aliasing techniques (including MSAA)

- Texture & Framebuffer Compression

- Hardware supported blending (normal alpha & linear color-space)

- Various texture and framebuffer formats

- 8 bit alpha/luminance, ARGB4444, ARGB1555, RGB565, ARGB8888 etc.

- Floating point texture support

- 3d texture and texture array support

- Frame buffers and textures up to 4k x 4k pixels

Software Drivers

TES provides Khronos conformant OpenGL ES 2.0 and EGL drivers. Both drivers rely on a low-level D/AVE NX driver layer, abstracting hardware details like register access and making porting to different CPUs / Operating systems easy.

All drivers have the following features:

- Fully reentrant & thread-safe

- Minimal OS dependency (HAL part separated)

- No inline assembler required

- Support for multiple D/AVE NX instances

- Multi-threading support, i.e. multiple applications can use D/AVE NX concurrently

- Small memory footprint

Block Diagram

What’s Included?

- VHDL (IP Core) including test bench

- OpenGL ES 2.0 driver under Linux

- Documentation

- PC based pixel exact emulatior

- Ready to use demos (as source code)

- FPGA Evaluation Kit (optionally)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about GPU IP core

Power, Not Area: Why Edge GPU Design Is Entering a New Era

What Does a GPU Have to Do With Automotive Security?

How Alternate Geometry Processing Enables Better Multi-Core GPU Scaling

Desktop-Quality Ray-Traced Gaming and Intelligent AI Performance on Mobile with New Arm Mali G1-Ultra GPU

NVIDIA GPU Confidential Computing Demystified

Frequently asked questions about GPU IP cores

What is OpenGL ES 2.0 3D graphics IP core for FPGAs and ASICs?

OpenGL ES 2.0 3D graphics IP core for FPGAs and ASICs is a GPU IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this GPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.